En av de största förändringarna gjordes 2005, då Synopsys tvingades ta hänsyn till att vid geometrier runt 130 nm och därunder dominerade fördröjningarna i ledarna över fördröjningarna i grindarna, vilket ställde de tidigare syntesalgoritmerna på ända. Då infördes även så kallad framåtseende optimering (look-ahead optimization) som gjorde att syntesresultatet avseende timing, yta och effekt hamnade inom 10 procent av det slutgiltiga kislets egenskaper.

Nu, då det är geometrier på 32 nm och finare som gäller, har nya problem tillkommit. Ett exempel är att den totala ledarlängden per ytenhet har mer än fördubblats, vilket ställer ännu högre krav på att algoritmerna tar hänsyn till ledarfördröjningarna. Samtidigt sitter många kretselement allt närmare varandra, vilket ökar kapacitanserna dem emellan (coupling capacitance). Och den 10-procentiga noggrannheten räcker inte längre - många kunder kräver bättre. Dessutom finns ett starkt önskemål om ökad produktivitet, där syntes och det mer fysiska arbetet med placering och ledningsdragning går mer hand i hand.

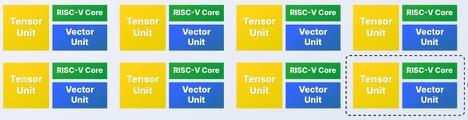

Så beskriver Synopsys problemställningen, och i Design Compiler 2010 leverera man ett förslag till lösning. En del av lösningen är stöd för datorer med multikärnor, vilket dubblar exekveringshastigheten på en fyrkärnig pc. Vilket kan tyckas som en måttlig ökning, men faktiskt är ett stort framsteg.

– Många delar av syntesarbetet lämpar sig inte för parallellisering och multikärnor. Men vi har skrivit om en stor andel av algoritmerna så att de nu även är skalbara för kommande datorer med 8 och 16 kärnor, säger Gal Hassan på Synopsys till Elektroniktidningen.

Därutöver, och kanske viktigare för produktiviteten, finns bättre koppling till den fysiska syntesen i systerprogrammet IC Compiler, allt i avsikt att reducera antalet iterationer. Exempelvis kan en grov ytplanering – floor plan – göras med en knapptryckning.

– Tidigare var många konstruktörer skeptiska till ytplanering, men nu är det mer accepterat. Att kunna göra syntes och påföljande ytplanering på detta sätt minskar den totala utvecklingstiden ordentligt, säger Gal Hassan.

Tack vare bättre modellering och omskrivna algoritmer har noggrannheten ökat till 5 procent för yta och timing. Dock ligger den kvar på 10 procent för effekten.

Totalt säger Synopsys att nyheterna dubblerar konstruktörernas produktivitet, något man fått stöd för hos en del tidiga användare av programmet.