Alteras nästa generation FPGA:er, som ska tillverkas i TSMC:s 28-nm process, är designade för maximal bandbredd. Det gäller allt från Serdesblocken som klarar upp till 28 Gbit/s till de skalbara DSP-blocken som går från 9x9 upp till 54x54 bitar.

Alteras nästa generation FPGA:er, som ska tillverkas i TSMC:s 28-nm process, är designade för maximal bandbredd. Det gäller allt från Serdesblocken som klarar upp till 28 Gbit/s till de skalbara DSP-blocken som går från 9x9 upp till 54x54 bitar.Med Stratix V ökar det maximala antalet logikblock till 1,1 miljoner (680k i förra generationen), RAM-minnet går från 22,4 Mbit till 53 Mbit, det maximala antalet multiplikatorer (18x18) ökar från 1360 till 3680 stycken och det maximala antalet Serdesblock går från 48 till 66. Och så finns två Hadcopyblock vilket motsvarar ytterligare cirka 700 000 logikelement eller 14 miljoner asicgrindar.

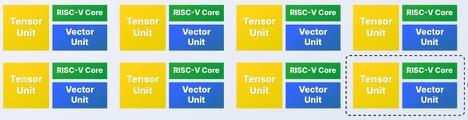

Men allt får inte plats i samma krets så Altera har skapat fyra smaker av Stratix V. Det är GT som innehåller de snabbaste Serdesblocken på 28 Gbit/s. GX har Serdesblock som går från 600 Mbit/s upp till 12,5 Gbit/s. GS innehåller förutom samma Serdesblock som GX också multiplikatorer. Slutligen finns E-modellen. En klassisk FPGA med maximalt antal logikblock och utan Serdes-moduler.

Alla varianter utom E-modellen innehåller dessutom två Hardcopyblock men än så länge använder Altera dessa för en del av implementationen av Serdesblocken.

– Det ger bättre flexibiliteten vilket behövs eftersom alla standarder för de snabbaste bussarna inte är låsta än, säger Bob Blake på Altera.

Så småningom kommer dock Hardcopyblocken att kunna användas fritt av kunderna för att egna konstruktioner.

En av nyheterna i Stratix V är att det går att konfigurera ordlängden i multiplikatorerna i sex steg från 9x9, via de klassiska 18x18 upp till 54x54 bitar.

– I videotillämpningar är det populärt med 9x9 eller 18x8 medan man för trådlös kommunikation använder 18x18 eller 18x36 bitar. Sen vill framförallt militären ha ändå bättre upplösning, säger Bob Blake.

Kretsarna har också fått inbyggt stöd för flyttalsoperationer. En annan nyhet är att Stratix V stödjer DDR3-minnen med en bandbredd på 1 600Mbit/s, eller 7 x 72-bitar men även LVDS-protokollet upp till 1,6 Gbit/s.

Trots alla förbättringar av prestanda ska kretsarna ändå dra 30 procent mindre energi än sina föregångare.

En ny version av designverktyget Quartus II för 28 nm kommer under andra kvartalet, bland annat ska den hantera den partiella rekonfiguration som är en av nyheterna i Stratix V. De första kretsarna under kvartal ett nästa år.