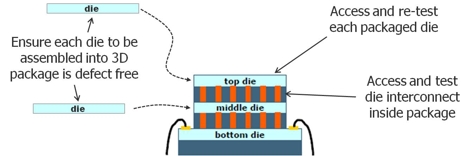

Ur testsynpunkt utgör sådana skapelser tre olika utmaningar. Den första är ekonomisk – det ställs mycket högre krav på att varje kiselbit testas ordentligt innan de monteras i kapseln eftersom det blir mycket dyrare att kassera en kapsel med tre chips, varav två fullt fungerande. De andra två är mer tekniska – efter kapsling måste såväl de övre kretsarna som de genomgående viahålen testas innan leverans. Dessa tester måste göras genom den undre kretsen, eftersom enbart denna har kommunikation med omvärlden.

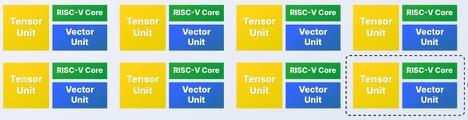

EDA-bolaget Mentor Graphics har löst den första utmaningen tidigare genom sitt verktyg Testkompress, som medger hög testtäckningsgrad samtidigt som behovet av minne i testarna minimeras. Nu har bolaget även löst de andra två utmaningarna, detta genom att stödja den utvidgning av Jtag-arkitekturen (IEEE 1149.1) för 3D som Imec föreslagit IEEE, samt utöka sitt testverktyg Tessent för att klara dessa testuppgifter. I arkitekturen ingår ett antal genomgående vior som enbart används för teständamål, av Mentor kallade "testhissar" då de "hissar upp" testerna till nästa nivå.

Något förenklat går tekniken ut på att de sedvanliga scanslingorna förlängs så att testmönster kan klockas genom hela konstruktionen, inte bara den undre kretsen. Tekniken gör det möjligt att återanvända all automatisk testmönstergenerering och inbyggda självtest som tidigare utvecklats, och applicera dessa genom Jtag-porten. För DRAM har företaget utvecklat särskilda programmerbara inbyggda självtester (Bist). Dessa kräver att logik för ändamålet, så kallad Mbist, finns inlagd på minneschipset.

När väl de genomgående viorna testats kan de ingående chipsen testas parallellt, vilket sparar tid.

Tekniken ingår i nästa version av testverktyget Tessent som når användarna i maj.