Japanska Renesas presenterar cpu-kärnor som använder den öppna instruktionsuppsättningen Risc V.

Japanska Renesas presenterar cpu-kärnor som använder den öppna instruktionsuppsättningen Risc V.

Nyheten idag är kärnorna i sig. Fysiska kretsar ska släppas Q1 2024 och provexemplar finns hos kund. Renesas har inte redovisat några planer på att licensera ut sina cpu-kärnor till andra företag.

Nyheten idag är kärnorna i sig. Fysiska kretsar ska släppas Q1 2024 och provexemplar finns hos kund. Renesas har inte redovisat några planer på att licensera ut sina cpu-kärnor till andra företag.

Renesas har sedan tidigare styrkretsar med Risc V-kärnor från taiwanesiska Andes. De sitter i ASSP-kretsar för röststyrning och motorstyrning.

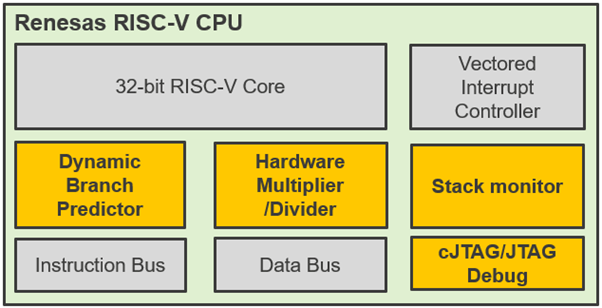

De egna kärnorna är 32-bitare med dynamisk grenprediktor, multiplikation/divison (M) och bitoperationer (B). De har stackmonitor, JTAG och stöder komprimerade (C) och atomära (A) operationer.

Renesas skriver mer om sina kärnor på renesas.com/risc-v.

De finns i två Risc V-profiler: RV32I med 32 register och den 25 procent mindre inbyggnadsprofilen RV32E med bara 16 register.

Renesas räknar upp styrkretsar för IoT, konsumentelektronik, hälsovård och industriella system som tillämpningsområden. Prestanda ska vara 3,27 Coremark/MHz.

Japanska Renesas levererar drygt 3,5 miljarder styrkretsar om året. De är 8-, 16-, 32- och 64-bitare. Hälften hamnar i fordon och merparten av resten i industriella applikationer, IoT och infrastruktur för datacenter och kommunikation.