Dagens kretsar innehåller funktioner som tidigare fanns utspridda i separata komponenter. Men hur verifierar man att systemkretsen fortfarande fungerar korrekt när det är dags att släppa ratten i en självkörande bil? IJTAG, eller Internal JTAG, löser problemet genom att extra register och logik adderas under konstruktionsfasen för att kretsen ska kunna testas under drift.

Dagens kretsar innehåller funktioner som tidigare fanns utspridda i separata komponenter. Men hur verifierar man att systemkretsen fortfarande fungerar korrekt när det är dags att släppa ratten i en självkörande bil? IJTAG, eller Internal JTAG, löser problemet genom att extra register och logik adderas under konstruktionsfasen för att kretsen ska kunna testas under drift.

– För 20 år sedan diskuterade man kiselkostnaden. Idag vill man inte ha ett liv på sitt samvete, säger Erik Larsson som är professor i Datorarkitektur vid Lunds universitet.

Han har forskat kring test av digitala system sedan slutet av 90-talet.

– Jag har alltid funderat på hur man ska göra designen. Ska man ha en högnivåbeskrivning eller ska man använda byggblock?

Den senare metoden kan sägas ha vunnit. Idag plockar man ihop en ny systemkrets med hjälp av färdiga IP-block.

– Köper du en Armkärna får du med testvektorer vilket är bra, men hur får du in dem från kretsens ben till kärnan? Det räcker inte med bara JTAG.

Dessutom används många kretsar i säkerhetskritiska tillämpningar vilket gör att det inte räcker med att testa dem en enda gång för att försäkra sig om att allt fungerar som det ska.

– Förr i världen var det helt ok att göra produktionstest, sen höll elektroniken i 20 år. Nu finns det processvariationer, åldrande och andra faktorer som har betydelse för livslängden.

Man måste helt enkelt utföra någon form av självtest med lämpliga intervall, speciellt när det handlar om elektronik för fordonstillämpningar.

|

|

Erik Larsson

|

– Om den här komponenten sitter i en bil och man måste testa att den fungerar under drift, vad har man då för möjligheter att komma åt det som finns inuti? Om ett fel uppstår någonstans i en krets, hur lång tid tar det innan information om detta finns vid kretsens ben?

Ett annat argument för att addera interna testinstrument i kretsarna är att många produkter har ett högt värde samtidigt som de är svåra att felsöka. Om exempelvis en basstation inte fungerar måste en servicetekniker åka ut för att undersöka problemet. Kortet byts antagligen ut och skickas sedan till en verkstad.

– Men det är inte säkert att man hittar något fel även om kunden säger att det inte fungerar.

Problemet behöver inte nödvändigtvis sitta i kretskortet, det kan vara något annat i systemet som spökar. I och med att korten är dyra vill man inte gärna slänga dem, de kan därför komma att skickas till en annan kund som kanske inte upplever några problem alls. Det kallas No Fault Found (NFF) eller No Trouble Found (NTF).

– Hela den här biten kostar väldigt mycket pengar. Här skulle man kunna gå in och samla information medan kortet sitter på plats för att se vad som händer. Sen kanske man kan säga att det inte är vår komponent som är trasig, säger Erik Larsson.

För att lösa den här typen av problem har vissa företag som designar kretsar använt JTAG även för att komma åt instrument som designats in i kretsarna, som temperatursensorer.

– JTAG används till både det ena och det andra men problemet är bristen på flexibilitet.

Det finns inget generellt sätt att beskriva exempelvis en temperatursensor i JTAG utan att samtidigt beskriva designen med alla dess funktioner. Och om man har många temperatursensorer, hur ska man koppla ihop dem? Hur mycket av det måste bestämmas i designfasen och hur mycket kan man lämna till användaren?

– Säg att det är tusen instrument som är tio bitar långa. Om de ligger i en seriell kedja kostar det mig tio tusen klockcykler varje gång jag vill klocka ut ett värde.

En annan parameter är att kunderna i många fall är intresserade av att veta hur det ser ut inuti kretsen för att kunna förstå vad som händer om något går fel. Den som designat kretsen är inte lika intresserade av att avslöja allt ner till transistornivå.

Dessa dilemman har bidragit till att IJTAG, Internal JTAG, skapades. IJTAG eller IEEE P1687 som det officiella namnet lyder, ger tillgång till interna instrument i kretsen. Det kan vara temperatursensorer, spänningsövervakning, brusmätning, feldetekteringskoder eller olika självtester. För att det ska fungera har man delat upp beskrivningen av instrumenten i två delar, PDL (Procedural Description Language) och ICL (Instrument Connectivity Language).

PDL beskriver syntaxen för hur man interagerar med instrumenten, exempelvis läser ut temperaturen eller gör inställningar.

ICL beskriver instrumentet men ger bara den information som behövs för att läsa och skriva till det. Det ger ingen information på RTL- eller grindnivå.

Med PDL och ICL får man en beskrivning av instrumenten, och hur de är sammankopplade, som går att lämna till kunden utan att avslöja exakt hur kretsen fungerar. Kunden kan i sin tur skapa tester som körs vid lämpliga tillfällen.

– Vi och andra grupper jobbat med frågan hur man gör hopkopplingen av sensorerna på ett smart sätt.

Ett av våra målet är att information om ett fel ska kunna läsas ut snabbare än en processorkärna hinner bearbeta data, helst på mindre än hundra klockcykler.

En av grundtankarna med IJTAG är att göra det så enkelt som möjligt att addera olika tester i existerande designflöden men också att modifiera dem.

– Ändrar du upplösningen i temperatursensorn en bit ska du bara behöva klicka i det, så ska det ske automatiskt, säger Erik Larsson.

Det kan vara vid start av systemet, men också under drift.

– Varken JTAG eller IJTAG stör funktionen i systemet, de sitter som en bakdörr och är ett utmärkt sätt att samla information om systemet.

Förklaringen är att bakdörren, det vill säga TAP-porten, inte används till något annat än just test under drift.

IJTAG antogs i december 2014 och precis som med JTAG har industrin varit lite avvaktande. Idag finns det stöd i EDA-jätten Mentors verktyg liksom hos konkurrenterna Cadence och Synopsis.

– Det finns nog en och annan som använder den med det tar en stund innan man förstår värdet. Jag tror att allt fler kommer att försöka skära ner kostnaderna för hanteringen kring No Fault Found och då är IJTAG ett bra hjälpmedel, säger Erik Larsson.

Han tror också att många kommer att vilja återanvända allt det arbete de lagt ner på verifiering av kretsarna under designfasen när kretsarna är tillverkade och det är dags att verifiera att prestanda är korrekt.

– Återigen, IJTAG skulle kunna underlätta. Och när 1687.1 kommer, och det inte längre behövs en dedikerad TAP-port, då är bordet dukat för att kunna se så att kretsar verkligen fungerar som de ska och att de gör det så länge de används.

Från test av kort till test av systemkretsar

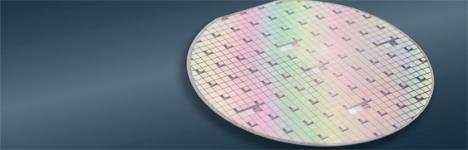

För sisådär 30 år sedan, när det började bli vanligt med ytmonterade komponenter, blev det mer eller mindre omöjligt att använda prober för att testa och felsöka. Anslutningarna satt antingen under kretsarna, som på BGA:er, eller så var benen så små och tätt placerade att det var svårt att komma åt med probspetsen.

Svaret stavades JTAG (Joint Test Action Group), även kallat Boundary Scan eller IEEE 1149.1. Det är en digital testmetod som togs fram för att göra det möjligt att kontrollera att komponenterna monterats korrekt på det färdiga kretskortet och att de hade förbindelse med varandra.

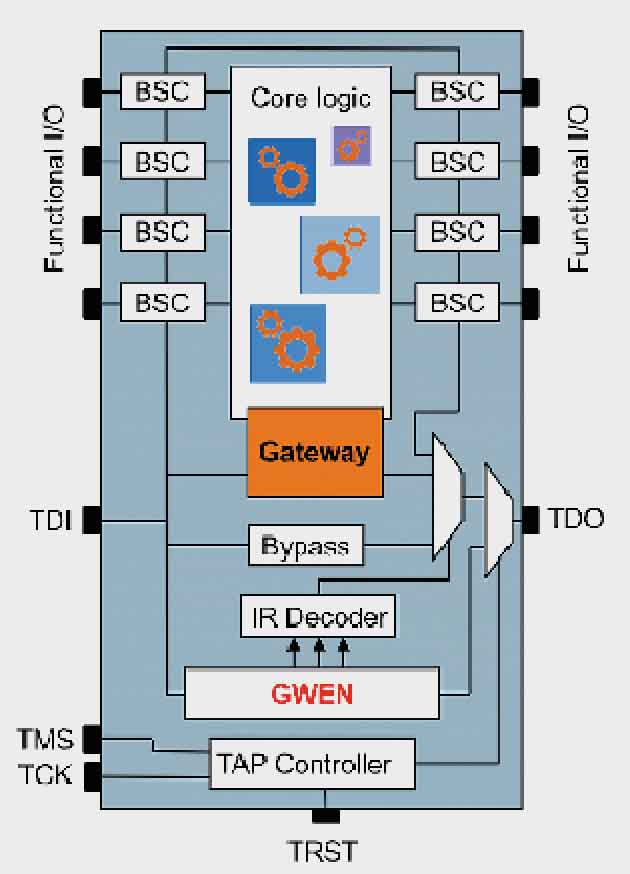

Tekniken förutsätter att det finns speciella register på ingångarna till de digitala kretsarna och dessutom en speciell port kallad TAP – Test Access Port – med två, fyra eller fem anslutningar beroende av version. TAP är en tillståndsmaskin som kan försätta kretsen i ett testläge varefter testvärden klockas in och resultaten hämtas ut.

När JTAG introducerades i början av 90-talet var ett vanligt argument att det använde en del av ytan på kretsen trots att långt ifrån alla kunder utnyttjade funktionen. Moores lag har gjort det till en ickefråga. Idag är det ingenjörskraften som är den stora kostnaden.

Artikeln är tidigare publicerad i magasinet Elektroniktidningen. Artikeln är tidigare publicerad i magasinet Elektroniktidningen.Prenumerera kostnadsfritt! |

Samtidigt har allt fler funktioner integrerats i en och samma krets. Dagens integrerade kretsar är gårdagens kretskort, vilket lett till svårigheter med att verifiera att kretsen verkligen fungerar som tänkt. I och med att alltfler digitala kretsar har en JTAG-port har vissa företag skapat interna tester baserat på den.

2005 kom IEEE 1500 som ett försök att standardisera dessa interna tester och 2014 klubbades IEEE 1687 eller Internal JTAG (IJTAG) som den också kallas. Bägge är komplement till IEEE 1149.1 och används för att testa innehållet i kretsarna.

IEEE 1687 använder en modifierad variant av TAP-porten där man kan skifta in kontrollbitar tillsammans med data. Därmed går det exempelvis att specificera vilket internt testinstrument man vill läsa av.

Samtidigt har arbetet med nästa version – 1687.1 – redan startar. Bland annat utreds om det är möjligt att använda USB- eller SPI-bussar för att ersätta TAP-porten, och därmed öka datatakten. Dessutom skulle det spara några anslutningar på kretsen. Frågorna handlar bland annat om vad som händer när data inte levereras synkront utan kommer som paket.

– Vad ska ingå i dessa, hur gör man med klockan, vad ska genereras på chippet, säger Erik Larsson.

Det finns en arbetsgrupp inom IEEE som tittar på detta.

– Jag är med och lyssnar för att se vad vi kan bidra med. I alla standarder finns det frihetsgrader och det är intressant att ta reda på vad de innebär, säger Erik Larsson och fortsätter:

– Vi kan göra analyser och fundera på begränsningar, samma saker som vi gjorde med 1687.