Lundabolaget Alixlab har verifierat sin metod att klyva transistorns fena vilket kan sänka kravet på litografin i de allra mest avancerade CMOS-processerna. Nu ska företaget ta in pengar för att kunna flytta tekniken till en tillverkningslina för 300 mm-skivor.

Lundabolaget Alixlab har verifierat sin metod att klyva transistorns fena vilket kan sänka kravet på litografin i de allra mest avancerade CMOS-processerna. Nu ska företaget ta in pengar för att kunna flytta tekniken till en tillverkningslina för 300 mm-skivor.

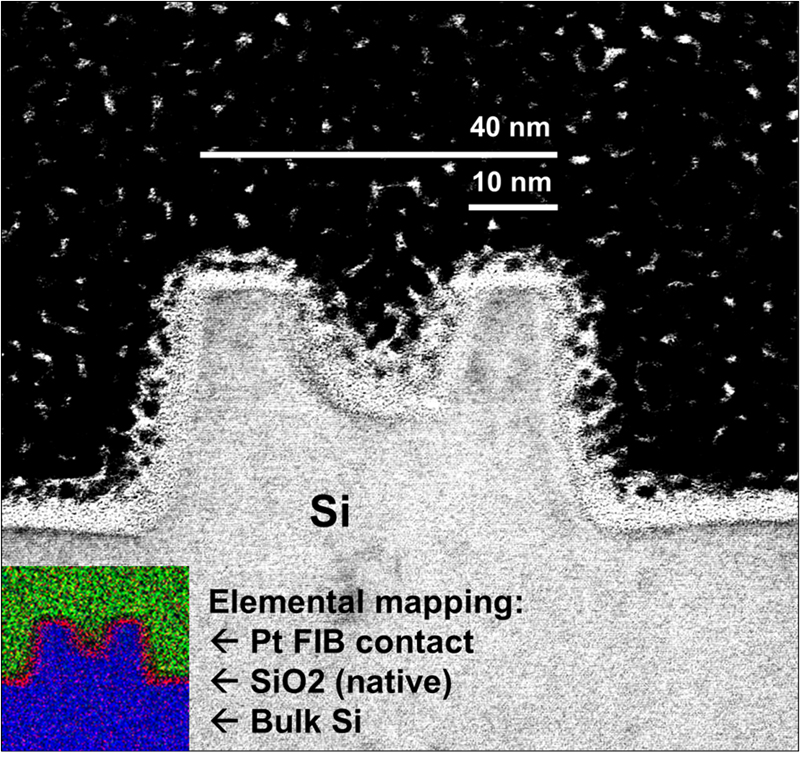

I ett försök med vanligt bulkkisel av typen P100 har företaget tillverkat en struktur på 40 nm som sedan delats upp i två stycken på 10 nm vardera med hjälp av en typ av torretsning kallad ALE, atomic layer etching.

I ett försök med vanligt bulkkisel av typen P100 har företaget tillverkat en struktur på 40 nm som sedan delats upp i två stycken på 10 nm vardera med hjälp av en typ av torretsning kallad ALE, atomic layer etching.

Förutom att uppdelningen gick bra med i princip vertikala kanter blev ytan på toppen slätare än före bearbetningen och det uppstod inga defekter i kristallgittret.

Alixlabs metod gör den så kallade struktureringen i tillverkningsprocessen vilket minskar kravet på litografin.

– Istället för att göra två exponeringar med EUV, en dubbelexponering, räcker det med en för att nå samma mål. Enkelt uttryckt kan man säga att vi från 14 nm kan göra 7 nm, sade företagets vd Jonas Sundqvist till Elektroniktidingen sommaren 2021.

Även om det är en förenkling – det finns många varianter på hur litografin görs – visar det på potentialen.

– Man kan köra immersionlitografi med double patterning och sedan lägga in vår metod eller börja med vår metod och sedan köra double patterning.

Detsamma gäller för EUV.

– Vilken ordning man väljer beror på designen. Vi jobbar mest med att göra själva fenan i FinFET-transistorn.

Företaget arbetar nu med att ta in pengar för att kunna flytta tekniken till en 300 mm-process, och därmed öppna för potentiella kunder att testa den under 2024.

Läs en längre artikel om Alixlabs här (länk).