Mindre programmerbar logik men fler hårda block för 5G-radion. Så kan man beskriva Zynq RFSoC DFE, den senaste medlemmen i Xilinx familj med systemkretsar som ska ta plats i de 5G-produkter som rullas ut nästa år.

Mindre programmerbar logik men fler hårda block för 5G-radion. Så kan man beskriva Zynq RFSoC DFE, den senaste medlemmen i Xilinx familj med systemkretsar som ska ta plats i de 5G-produkter som rullas ut nästa år.

– Vi har avvikit från den tidigare strategin för att få ned effektförbrukningen och öka integrationen, säger Gilles Garcia på Xilinx.

Zynq-familjen var ursprungligen en FPGA-krets där en mindre del av kiselytan upptogs av två Arm-kärnor plus att man kunde få snabb kommunikation med omvärlden. Under årens lopp har de hårda blocken fått ökat utrymme för att lyfta prestanda, bland annat har det kommit en modell med AD- och DA-omvandlare för rf-tillämpningar.

– Den version som kom 2018 gick upp till 4 GHz och sitter i många av de tidiga 5G-produkterna i bland annat Sydkorea.

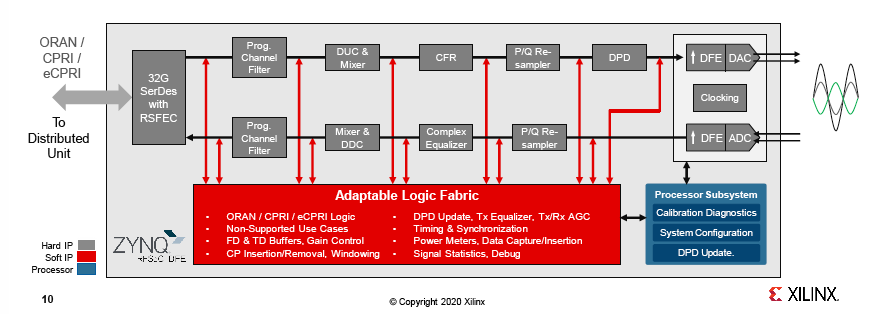

För att inte ersättas av asicar när volymerna nu ökar har Xilinx tagit fram hårda block för hela mottagar- och sändarkedjan plus att frekvensområdet ökat till 7,125 GHz (FR1). I Zynq RFSoC DFE, där DFE står för DFE, Digital Front End, upptar de större delen av kiselytan medan den programmerbara logiken får spela andrafiolen.

Samtidigt är kretsen designad så att det går att koppla bort alla hårda block och ersätta dem med kod som körs i den programmerbara logiken. Det öppnar för att hantera utvecklingen de nya versioner av 5G-standarden som släpps en gång per år men också produkter som behöver anpassas för en viss marknad eller tillämpning.

Kretsen stödjer en bandbredd på 400 MHz över åtta frekvensband i både upp- och nedlänken (8T8R).

För högre frekvensband, det vill säga FR2, kan ger kretsen en mellanfrekvensbandbredd på 1600 MHz.