Många som arbetar med fiberoptisk kommunikation oroas av trenden mot allt mer energislukande elektronik som krävs för att skapa framtidens allt högre datahastigheter. Inom ett stort tvärvetenskapligt projekt på Chalmers har Per Larsson-Edefors forskarteam konstruerat, tillverkat och testat felrättande asicar. Resultatet är överraskande positivt.

Många som arbetar med fiberoptisk kommunikation oroas av trenden mot allt mer energislukande elektronik som krävs för att skapa framtidens allt högre datahastigheter. Inom ett stort tvärvetenskapligt projekt på Chalmers har Per Larsson-Edefors forskarteam konstruerat, tillverkat och testat felrättande asicar. Resultatet är överraskande positivt.

Mängden data som skickas över fiberoptiska länkar ökar i ett rasande tempo. Framtida system kommer att behöva utnyttja bandbredden ännu mer. Då behövs komplex signalbehandling och avancerad elektronik för att driva datatrafiken.

|

| Per Larsson-Edefors |

– Många oroas över att den digitala delen, signalbehandling och felrättning, i kommande system ska kosta för mycket rent energimässigt, säger Per Larsson-Edefors, professor vid institutionen för data- och informationsteknik på Chalmers.

Inom projektet Energieffektiv optisk fiberkommunikation har hans forskargrupp tittat på asic-konstruktion både för felrättning och signalbehandling.

Resultaten visar att det är svårt att dra ner energiförbrukningen hos signalbehandlingen eftersom DSP-funktioner switchar konstant och filtrerar samt formar data i varje cykel. Inom felrättning har teamet däremot nått långt över förväntan.

– Vi har kunnat visa att det går att bygga felrättande asicar som drar en tiondel av vad man tidigare trott och vad vi sett publicerat.

– I vissa delar har vi nog dragit ner energiförbrukningen ännu mer än så och framförallt har vi byggt system som går fortare än någon annan har visat tidigare, över 1Tbit/s i simulering.

En viktig detalj är att skilja på effekt- och energiförbrukning. Effekt är hur många watt en komponent drar. Effekten ökar i takt med att kapaciteten ökar och är en praktisk parameter som anger hur du ska strömförsörja.

Energiförbrukningen kan istället användas för att jämföra olika konstruktionsalternativ. Då tittar du på energin som behövs per bit som du transporterar.

– Det är lite nytt för denna tillämpning. Området har varit drivet av industrin och många är vana att tala om just effekt, men energi per bit gör att vi kan jämföra olika typer av komponenter i ett system. Det kan vara att jämföra AD-omvandling med en rent digital lösning eller analogt med digitalt, förklarar Per Larsson-Edefors, och adderar:

– Samtidigt vill vi också kunna relatera vårt system till en datatakt. Då är det behändigt att använda energi per bit.

|

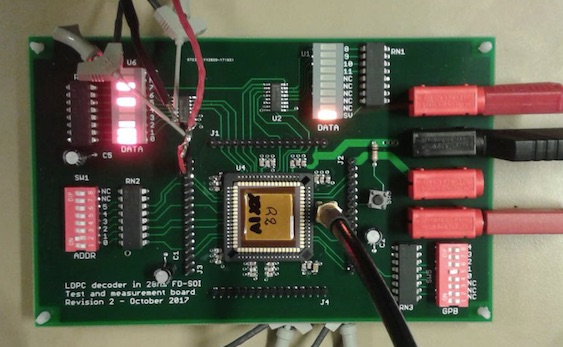

| En mätuppställning som testar ett av chipen i det beskrivna projektet. |

Tre felrättande asicar har teamet realiserat i kisel. Det första chipet är publicerat, ett körs just nu i labbet och ett fungerar inte helt enligt specifikationen – troligen har något gått snett i klockningen.

Chipet som hittills mäts upp är tillverkat i 28 nm och körs i 400 MHz. Det som snurrar i labbet är tillverkat i 22 nm.

– Det är det första akademiska digitala chipet i Sverige som är tillverkat i 22 nm, konstaterar Per Larsson-Edefors stolt.

Den första asicen är en så kallad mjuk avkodare. Den är komplex, men väldigt effektiv. Det är denna typ av felrättare som branschen traditionellt använder.

–En mjuk avkodare är bra på att göra omvandlingen från många fel till få fel. Den kan korrigera indata där var 100:e till 1000:e datasymbol är felaktig till utdata som i stort sett är fritt från fel.

Den senare varianten är lite mer åt det hårda hållet. Det gör den lite sämre på felrättning, men i regel mer effektiv när det gäller energi per bit.

Strävar efter effektivare kommunikationFör fem år sedan drog ett stort forskningsprojekt igång på Chalmers. Målet har varit att hitta de största energitjuvarna i fiberoptiska system samt att utveckla system och komponenter som förbrukar endast en tiondel av energin av dagens system. Nu lider det femåriga projektet mot sitt slut och inom vissa områden har det visat på verkligt imponerande resultat. De asicar med felrättande system som utvecklats av en forskargrupp ledd av professor Per Larsson-Edefors lyfts speciellt fram i detta sammanhang. En lärdom är att genom smart konstruktion går det att göra felrättning mycket energieffektivare än man tidigare trott. Knut och Alice Wallenbergs stiftelse har finansierat projektet med nära 34 miljoner kronor. |

De olika egenskaperna förklaras av att en mjuk avkodare behöver arbeta längre än en hård för att utvinna information. Den mjuka använder felsannolikhetsnivåer i data och behöver exempelvis en mer avancerad AD-omvandlare. Den måste fundera på vilka sannolikheter det finns att det är en etta eller nolla i kanalen, medan en hård bestämmer sig för att det antingen är ett eller noll.

Mjuka avkodare används i regel på långa dyra fibrer med stor effektbudget, där kan man offra energi och effekt. De hårda är mer anpassade till snålare system.

Felrättaren som jobbar i Chalmerslabbet just nu är en utvidgning på detta koncept. Den har en hård kärna med mjukt gränssnitt.

– Ännu har vi inte sammanställt data som vi samlat in, men antagligen kommer det senaste chipet att ha ännu lägre energi per bit än vårt första.

Att forskarna valt att realisera felrättande kretsar i kisel, och inte DSP-kretsar, har sin logiska förklaring.

– Orsaken är att de fysiska kretsarna som vi har byggt i detta projekt är väldigt enkla att testa i den meningen att vi kan bygga testlogik direkt på chipet.

– Vi behöver egentligen bara starta chipet och styra det med en klocka och några enkla kontrollsignaler. Hela testförfarandet blir mycket enklare än om vi skulle behöva mata in och ut data med en testutrustning. Det är väldigt bandbreddsbegränsande och gör av med många ben och chip-paddar.

För att skapa kanaldata som har fel med en viss sannolikhet har forskarna byggt en syntetisk testrigg. Det är inte trivialt, men går att göra. Bruset i en fiber är normalfördelat, så det är lätt att beskriva rent matematiskt.

– Det gör att vi kan rigga en testutrustning på chipet som emulerar en kanal med detta brus. Sen gör vi några smarta tricks så att vi kan variera signal-brus-förhållandet. Ovanpå detta för vi in lite fel då och då. Vi kör i realtid så vi kan mäta energi, effekt och annat.

Vid test av DSP:er går det inte att använda samma tillvägagångssätt eftersom DSP:er arbetar på vågformer. Det är svårt att skapa realistiska vågformer, och ännu mycket svårare att skapa meningsfulla vågformer syntetiskt. När forskarna konstruerar DSP:er använder de sig istället av simulerade modeller.

– En annan anledning att vi tittar på felrättning är att det är så extremt beräkningskrävande. För att skaffa statistik behöver man köra väldigt länge.

Denna artikel har tidigare publicerats i magasinet Elektroniktidningen. För dig som jobbar i den svenska elektronikbranschen är Elektroniktidningen gratis att prenumerera på – våra annonsörer betalar kostnaden. Denna artikel har tidigare publicerats i magasinet Elektroniktidningen. För dig som jobbar i den svenska elektronikbranschen är Elektroniktidningen gratis att prenumerera på – våra annonsörer betalar kostnaden.Här tecknar du prenumeration (länk). |

Framåt ser Per Larsson-Edefors det som en pedagogisk utmaning att få andra forskare att lämna det han kallar bekvämlighetszon av Matlab-användande.

– Ett problem är att nästan alla som idag jobbar med felrättning och DSP är algoritm- och Matlab-experter. Väldigt få forskare och utvecklare klarar att samtidigt jobba med kretsimplementation, men man måste faktiskt titta på praktiska system för att kunna beskriva effekt- och energikonsekvenser.

Han menar att problemet ligger i att algoritmer som skapas i Matlab inte har en stark koppling till elektroniken. Istället kan utvecklare, på gott och ont, utnyttja alla de frihetsgrader som Matlab-miljön ger. Det finns helt enkelt begränsat med hårdvarutänk bakom algoritmbyggandet.

– När Matlab ursprungligen lanserades kunde forskare och utvecklare hårdvara ganska bra men i takt med utvecklingen har man förlorat förståelse för hårdvaran bakom. Vårt projekt har visat att det finns stor potential att bygga smarta algoritmer som är bra för hårdvaran.

Inom projektets ramar har tre traditionellt åtskilda forskningsfält på Chalmers samarbetat: optisk hårdvara, elektronisk hårdvara och informationsteknik.

– Vi har inspirerat varandra och upptäckt både möjligheter och begränsningar. Bland annat att man kan ta sig ut ur Matlabs miljö, som är väldigt förenklande, till en hårdvarumiljö där man faktiskt kan analysera och mäta effekt och energi och se konsekvenser av designbeslut tagna på systemnivå.