Som redan har meddelats i Elektroniktidningen har Gordon Moore gått bort. Vi kommer alltid minnas honom för Moores lag, som förenklat säger att antalet transistorer på en given yta fördubblas på ungefär två år.

Som redan har meddelats i Elektroniktidningen har Gordon Moore gått bort. Vi kommer alltid minnas honom för Moores lag, som förenklat säger att antalet transistorer på en given yta fördubblas på ungefär två år.

Över tid leder det till stora mängder transistorer enligt nedanstående räkneexempel:

På tio år har vi fem dubblingar, eller 2x2x2x2x2=25=32 gånger.

På tjugo år har vi tio dubblingar, 210=1 024 gånger så många transistorer (låt oss räkna med 1 000 för enkelhets skull).

På fyrtio år har vi 1 000x1 000 = en miljon gånger fler transistorer, och på femtio år cirka 32 miljoner fler.

TACK VARE MOORES LAG har industrin gemensamt lyckats hålla den takten med tillverkningsmaskiner, design av integrerade kretsar som använder transistorerna, och tillverkningsuppfinningar för att göra transistorerna mindre.

Exempelvis hade Intels första integrerade krets 4004 från 1971 cirka 2 000 transistorer, femtio år senare hittar vi FPGA:er med cirka 60 miljarder transistorer.

Att det är dubbelt så många transistorer på samma yta är en viktig poäng. Om chipstorleken skulle ökat, från 1x1 cm 1971, skulle chippen 1991 varit 30x30 cm, och 2011 10x10 meter. Transistorytan minskar med hälften för varje två år, men med inversen av kvadratroten ur två av längden i båda dimensioner. Industrin har gått från en typisk gatelängd på 10 mikrometer till 10 nanometer för en faktor en miljon fler transistorer.

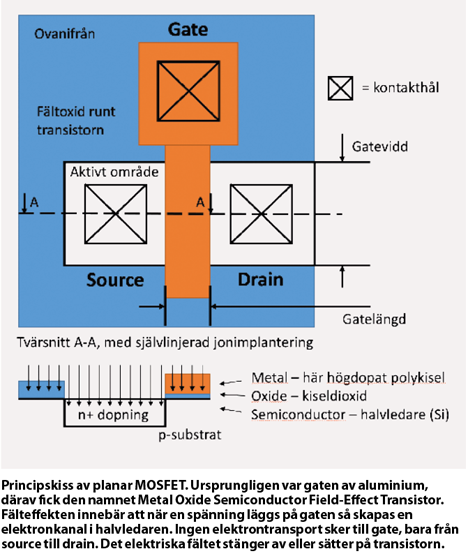

DET MAN KANSKE GLÖMMER att fråga sig är hur precisionen i tillverkningen kunnat öka med mer än en faktor 1000. Vid tillverkning av integrerade kretsar tillverkas alla transistorer samtidigt med fotolitografi. Denna process uppfanns 1958 av Lathrop och Nall, och ihop med planarprocessens uppfinnande av Hoerni 1959, var detta nödvän-diga men inte tillräckliga verktyg för de integrerade kretsarnas frammarsch. Det krävs flera steg i tillverkningen, där fotomaskens placering måste linjeras med föregående stegs resultat på kiselskivan. Ett viktigt val tidigt gjorde stor skillnad: istället för bipolärtransistorn valdes MOS-transistorn. Det gjordes dels för att den är energisnålare, dels för att den enklare kan krympas. Konceptet kallas skalning och tekniken för självlinjering.

Energisnålheten är viktig, med en miljard transistorer så får transistorerna inte förbruka mer energi per yten-het. Transistorskalningsprincipen av Dennard 1974 medför att varje transistor förbrukar mindre energi; i proport-ion till storleken. Annars skulle chippen, och mobiltelefonen brinna upp.

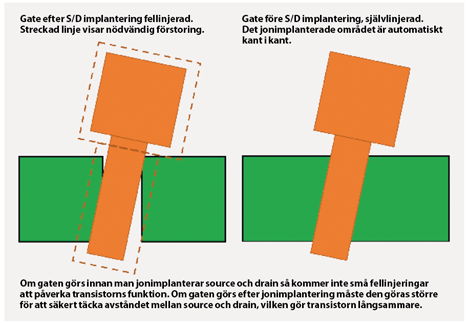

MED SJÄLVLINJERING UTNYTTJAS ett eller flera tidigare steg för att ge en mönstringsprecision som är bättre än om vi använder en fotolitografisk mask. Den minsta laterala dimensionen i en MOS-transistor är gatelängden, som avgör hastigheten och strömdrivningsförmågan. Gaten behöver passas in exakt över source och drainområdena, som är jonimplanterade. Genom att tillverka gaten före source och drain, och sedan använda kanterna på gaten som en självlinjerad mask för source och drain, kan passningen göras exakt, oavsett om gatelängden varierar, eller om gateområdet har en liten förflyttning eller vridning på chippet. Source och drain-områdenas utbredning bestäms även av en annan tidigare mask som definierar det aktiva områdets utbredning.

DET VIKTIGA STEGET var att utnyttja högdopat polykristallint kisel som gatematerial. Det har en bra ledningsförmåga, nästan metallisk, och tål den höga temperatur som krävs efter jonimplantering, ca 1 200°C. Tidigare användes en aluminiumgate, men aluminium smälter redan vid 660 °C. Processen kallades silicon-gate technology (SGT). Flera uppfinnare var involverade, men Federico Faggin på Fairchild brukar nämnas som den som gjorde den kommersi-ell 1968. Den var senare nyckeln i Intels 4004-processor.

DEN PROCESS SOM ANVÄNDES under flera år får då följande steg:

• deponering av isolationsoxid över hela kiselskivan

• öppning av aktivt område

• gateoxidering, ger en tunn isolerande oxid på aktiva området

• deponering av polykristallint kisel över hela kiselskivan

• mönstring av gaten i polykristallint kisel

• jonimplantering av source och drain, självlinjerat till isolationsoxiden och den polykristallina gaten

• värmebehandling vid 1 200 °C för att läka jonimplanteringsskador och aktivera dopämnena DETTA FÖLJS av flera metall- och isolationssteg för att koppla ihop transistorerna. I en CMOS-process tillverkas även p-kanals transistorer med p+ source och drain. I moderna kretsar används en icke-planar struktur som kallas FinFET för att ytterligare minska ytan som varje transistor upptar, och flera andra processknep.

DETTA FÖLJS av flera metall- och isolationssteg för att koppla ihop transistorerna. I en CMOS-process tillverkas även p-kanals transistorer med p+ source och drain. I moderna kretsar används en icke-planar struktur som kallas FinFET för att ytterligare minska ytan som varje transistor upptar, och flera andra processknep.

Artikeln är tidigare publicerad i magasinet Elektroniktidningen. Artikeln är tidigare publicerad i magasinet Elektroniktidningen.Prenumerera kostnadsfritt! |

Andra transistortyper som bipolärtransistorn har inga naturliga självlinjeringar som tillåter den att skalas så enkelt. Effektförbrukningen är också högre för bipolärtransistorer. När vi talar om att våra integrerade kretsar blir bättre i takt med Moores lag, menar vi i själva verket att MOS-transistorerna skalas enligt Dennards princip och med självlinjerad tillverkning som Faggin med flera utvecklade för 50 år sedan.