Avsaknaden av en standard har gjort att SiP:ar eller System-in-Package byggts med chiplets från en och samma tillverkare. Enda undantaget har varit minneskuber där det funnits en Jedec-standard.

In kommer Universal Chiplet Interconnect Express – UCIe 1.0. Det handlar om specifikationen till en öppen kommunikationsstandard som först utvecklades av Intel, men vilken företaget den 2 mars 2022 donerade till det som kom att bli UCIe-konsortiet.

In kommer Universal Chiplet Interconnect Express – UCIe 1.0. Det handlar om specifikationen till en öppen kommunikationsstandard som först utvecklades av Intel, men vilken företaget den 2 mars 2022 donerade till det som kom att bli UCIe-konsortiet.

Intel har varit ansvarigt för den ursprungliga utvecklingen av flera välkända, öppna standarder under åren. Du kanske känner igen USB, PCIe och Thunderbolt 3, så det är inte alltför konstigt att det nu släpper ytterligare en standard för att få fler att använda chiplets.

Intel har skaffat sig vapenbröder till UCIe, nämligen flera av de stora tillverkarna, AMD, Arm, ASE Group, Google Cloud, Intel, Meta, Microsoft, Qualcomm, Samsung och TSMC. Det finns alltså en betydande kraft bakom standarden.

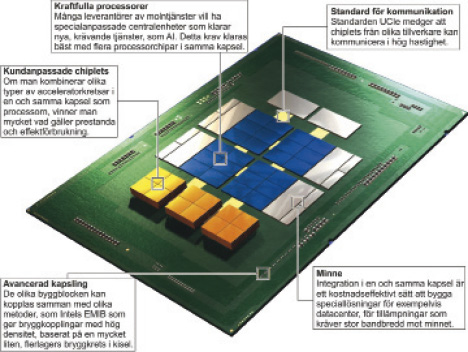

Man kan inte riktigt säga att Moores lag lirar på sista versen. Men den är inget kinderägg längre även om utvecklingen går vidare och man fortfarande får fler transistorer för varje ny processgeneration. Vill man ha verklig fart på utvecklingen av stora system är lösningen ändå att kombinera flera chip i samma kapsel.

Ett tidigt exempel på en SiP är Xilinx FPGA Virtex-7 2000T från 2011 som bestod av fyra kiselbitar (chiplets) tillverkade i en 28 nm-process. Resultatet var en krets med två miljoner logikceller.

Intel och AMD är två andra halvledarbolag som länge använt den här typen av byggsätt för sina vassaste processorsystem.

Standarden fastställer följande:

•Den fysiska kommunikationen mellan chiplets

•Kommunikationsprotokollen mellan chiplets

•En programvarumodell som drar nytta av de befintliga specifikationerna PCI Express (PCIe) och Compute Express Link (CXL).

PCIe känner vi igen som en standard för att kommunicera mellan utbyggnadskort i persondatorer, som skapades av Intel. CXL är en standard för kommunikation mellan processor, minne och andra snabba periferienheter, delvis baserad på PCIe, även denna framtagen av Intel.

En gemensam standard har den fördelen att konstruktörer kan blanda chiplets från olika leverantörer när de ska sättas samman till större system. De kan dessutom vara tillverkade i olika processer optimerade för den specifika uppgiften.

Resultatet blir större flexibilitet i utvecklingsarbetet. Det ger också en möjlighet att enklare kunna specialutveckla sådana system, snarare än att tvingas köpa chiplets från en och samma tillverkare och kanske få ett sämre urval.

Fördelarna med UCIe:

•Det går att skapa SoC som är större än gängse litografimasker tillåter

•Utvecklingstiden kan minskas

•Hela produkt- och projektkostnaden kan minskas

•Anpassningsbara produkter baserade på standard-chiplets blir möjliga

•Mera innovation, enklare

Samtidigt drivs det pågående intresset för chiplets av ett ständigt behov av ökande prestanda och effektivitet. Detta har resulterat i en önskan att integrera fler funktioner i en enda kapsel.

PCIe-bussen, hur snabb den än var, är fortfarande långsam enligt moderna bedömningar. De förhållandevis långa ledningslängderna från en kapslad processor via kretskortet till ett kapslat minne (och tillbaka igen) skapar en hel del latens, och det är relativt dyrt att driva data så långt. Så kretstillverkarna vill i allt högre grad stoppa in alla sådana funktioner i en enda kapsel, för att både minska latensen och strömförbrukningen.

|

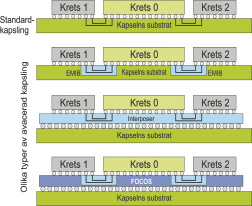

| Dessa typer av kapslingar kallas för 2D eller 2,5D-kapsling. •EMIB (Embedded Multi-Die Interconnect Bridge) är Intels uppfinning, en kiselbaserad tvärförbindelse som kan bäddas in i substratet. •En interposer är ett mellanlager i kisel med standard-kisel-vior avsett för tvärförbindelser mellan kretsar, en uppfinning av TSMC. •FOCOS betyder Fan-Out Chip on Substrate och är en typ av mellankopplingslager i kisel med korta kopparledare, uppfunnen av ASE Group, som ger lägre resistans, kortare ledare och lägre impedanser än en interposer. •Avstånden mellan kontaktpunkterna (bollarna, bumps) är av stor betydelse för hur hög överföringskapacitet man kan uppnå. |

I fallet med chiplets på en interposer (och därmed UCIe) innebär det enligt förespråkarna att det går att uppnå 20 gånger bättre I/O-prestanda till en tjugondel av effekten jämfört med att bygga samma system med separat kapslade kretsar.

Det finns olika metoder att kapsla och koppla ihop chiplets, allt efter vem som utvecklat metoderna.

Det finns i huvudsak två standardnivåer för kapslingens prestanda och komplexitet. Standardkapslingen är inte mycket mer än vad man tidigare gjort och är avsedd för enheter med lägre bandbredd, och byggs upp på traditionella, organiska substrat. Dessa typer föreslås nyttja upp till 16 dataledningar, mer än 100 mikrometer mellan kontaktpunkterna och långa kanallängder. Vill man, kan man se det som att man ansluter två enheter över en modern PCIe-länk, men att de är placerade mycket, mycket närmare varandra.

En andra uppsättning specifikationer utgör vad UCIe-gruppen kallar ”avancerade kapslingstyper” och i dessa används flera olika kiselbaserade tvärförbindelser med hög densitet, som EMIB och InFO. I specifikationen för ”avancerade kapslingar” krävs mindre avstånd mellan kontaktpunkterna – i storleksordningen 25 μm till 55 μm – såväl som fyra gånger så många ledningar per överföring, tack vare den högre packningstätheten och den korta räckvidden på under 2 mm.

Drivet till sin spets, menar UCIe-gruppen att man med dagens teknik och med 45 μm mellan kontaktpunkterna skulle kunna uppnå 1,3 TB per sekund vid en millimeters ledningslängd.

Det är intressant att notera vad standardgruppen förväntar sig när det gäller latens och energieffektivitet. Latensen förväntas ligga under 2 ns i alla kapseltyper, vilket är särskilt viktigt i konstruktioner med chiplets där man ju delar upp det som tidigare varit en enda monolitisk krets i mindre delar.

Energieffektiviteten sträcker sig från blygsamma 0,5 pJ/bit för standardkapslar, till det ännu lägre 0,25 pJ/bit för ”avancerade kapslingar”. Då blir det plötsligt väldigt lätt att förstå varför olika tillverkare är så angelägna att börja med chiplets, då förbättringarna jämfört med diskreta PCIe-CXL-kort kan vara betydande.

Utvecklingsgruppen har gjort klart att UCIe på intet sätt är inlåst i bara PCIe och CXL. Framtida versioner av standarden kan mycket väl komma att innehålla andra, bättre protokoll om något nytt, spännande skulle visa sig, och ägaren är villig att donera detta till standarden.

Artikeln är tidigare publicerad i magasinet Elektroniktidningen. Artikeln är tidigare publicerad i magasinet Elektroniktidningen.Prenumerera kostnadsfritt! |

I slutänden kan tillverkarna givetvis använda sina egna protokoll. Det finns inget krav att hålla sig till enbart PCIe och CXL. I UCIe ingår till exempel ett strömningsprotokoll som medger att valfritt protokoll används ovanpå detta. I så fall måste givetvis chipletsen i båda ändarna av förbindelsen ha stöd för dessa protokoll för att kunna kommunicera, men avsikten med det är trots allt att låta varje tillverkare dra nytta av UCIe för att förenkla sin egen konstruktionsprocess.

Läs mer: www.uciexpress.org