Få grindar och liten energiförbrukning är fördelarna som Toshiba framhäver med sitt experimentella chip, som hoppas på medvind från det stora intresset för AI-tekniken deep learning.

Få grindar och liten energiförbrukning är fördelarna som Toshiba framhäver med sitt experimentella chip, som hoppas på medvind från det stora intresset för AI-tekniken deep learning.

Inte nog med att chipet arbetar analogt, det är dessutom något så ovanligt som tid som är den analoga dimension som representerar datavärden i chipet. I konstruktionen ingår både tid-digital-omvandlare och digital-tid-omvandlare för att chipet ska kunna gränssnittas till den digitala världen. TDNN (Time Domain Neural Network) kallar Toshiba tekniken.

Artificiell intelligens i strömsnåla IoT-ändnoder är den tillämpning som Toshiba siktar på.

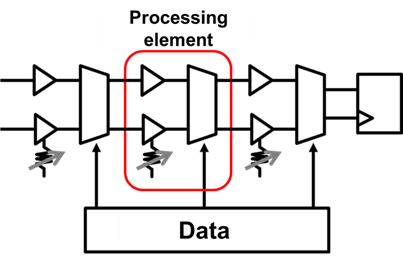

Toshibas proof-of-concept-chip använder SRAM-celler som minne. Ett beräkningselement består av tre logiska grindar och en minnesbit.

Datavärden, neuronnätets så kallade ”vikter”, lagras lokalt i beräkningsnoden, avslöjas i Toshibas pressmeddelande. Det är en av hemligheterna till strömsnålheten, att den slipper skyffla data till och från ett externt minne.

21 femtojoule är den energi som en operation gör av med. Konventionella kretsar gör enligt Toshiba av med sex gånger mer, och den skillnaden tror Toshiba kommer att växa i senare generationer av TDNN-tekniken. Nästa steg är att bygga ett TDNN-chip av ReRAM vilket dessutom ska krympa fotatrycket.

Chipet tillämpades på uppgiften att känna igen kinesiska skrivtecken, och där satte till och med Toshiba ett nytt rekord i precision – felfrekvensen halverades jämfört med det tidigare rekordet.

Tekniken att låta data representeras av tid presenterades redan år 2013 av Toshiba och kallas TDAMS3 (time-domain analog and digital mixed signal processing). Tiden som används för att representera värden, beskrivs av Toshiba som tidsfördröjningen av den digitala signalen när den passerar grinden.

TDNN presenterades tidigare idag på IEEE-konferensen A-SSCC (Asian Solid-State Circuits Conference) i Japan.