Super-FPGA med tid i arkitekturen

Super-FPGA med tid i arkitekturen

Genom att använda tiden som en tredje dimension har amerikanska Tabula tagit fram en FPGA med tätare logik och minne, och som ger upp till fyra gånger högre DSP-prestanda. Företaget har ännu inte lanserat en enda produkt, men har ändå lyckats locka nära en miljard kronor i riskkapital.Kretsen kan, tack vare den tillhörande kompilatorn, dynamiskt omkonfigurera såväl minne som logik i GHz-takt. En stor poäng är att ledningarna mellan logikblocken kan göras mycket kortare än i konventionella tvådimensionella FPGA:er.

– Nästan 90 procent av ytan i en FPGA används för ledningsdragning. Det driver upp storlek och kostnader, och begränsar också prestanda och möjlighet att få en konstruktion att nå den timing man tänkt. Om man ska nå ett kapacitetsgenombrott med rimliga kostnader så måste man effektivisera ledningsdragningen, och det är vad vi gjort, säger Steve Teig i ett pressmeddelande.

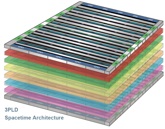

Arkitekturen har döpts till Spacetime, och företaget tänker nu ta fram kretsar som bygger på denna, av en typ man döpt till 3PLD, 3D Programmable Logic Devices. De ska göras i vanliga CMOS-processer i 40 nm - den tredje dimensionen har alltså inget med avancerade byggsätt på höjden att göra, utan avser tiden. Sett som kisel är dessa kretsar lika platta som andra.

Företaget beskriver arkitekturen som ett antal lager, eller "veck" (folds) som man föredrar att kalla dem. Varje veck utför en andel av den önskade funktionen, och lagrar resultatet lokalt. När några eller alla veck rekonfigureras så används lokalt sparat data för att utföra nästa del av funktionen. Genom att snabbt rekonfigurera för att exekvera olika delar av varje funktion kan en Spacetimekrets implementera en komplex konstruktion med betydligt mindre resurser än vad normala 2D-kretsar kräver.

Med arkitekturen säger sig Tabula nå 2,5 gånger högre logiktäthet, dubbelt så höt minnestäthet, nära tre gånger så många minnesportar och upp till 4 gånger högre DSP-prestanda.

En stor poäng som Tabula framhåller är att konstruktörerna kan använda sina vanliga EDA-verktyg. Den egenutvecklade kompilatorn utgår från vanlig RTL-kod - någon handpåläggning eller modifiering ska inte behövas.

Att ta sig in i den lönsamma FPGA-nischen är dock inte gjort i en handvändning. Trots otaliga försök - uppemot 50 företag har gjort större eller mindre ansatser här - är det alltjämt Xilinx och Altera som närapå delar marknaden mellan sig, med Lattice som distanserad trea. Och Tabula är inte ensamt om nya arkitekturer, nystartade Achronix (länk) drog igång produktion av sin 1,5 GHz FPGA i vintras, och Siliconblue (länk) som satsar på strömsnåla FPGA:er har också nyligen lanserat kretsar.

Tabula har dock lyckats få med sig namnkunniga investerare. Nära en miljard kronor har satsats i bolaget, från riskkapitalister som Benchmark, NEA, Greylock och Crosslink. Ambitionen är att bli industriledande.

Förutom Steve Teig och Dennis Segers finns en rad andra personer i bolaget med bakgrund från Xilinx, Altera och flera EDA-bolag.

Än så länge har företaget bara tagit fram protypkretsar, som dock visar att arkitekturen håller måttet. Man vill inte uppge när de första kretsarna ska lanseras på marknaden.