Ett sidoprojekt som blev toppresultat. Så kan man beskriva metoden som några forskare från Linköpings universitet efter en krokig väg äntligen fått publicerat av IEEE. Deras byggblock – en FFT-kärna – är fem gånger bättre än bästa alternativ.

Ett sidoprojekt som blev toppresultat. Så kan man beskriva metoden som några forskare från Linköpings universitet efter en krokig väg äntligen fått publicerat av IEEE. Deras byggblock – en FFT-kärna – är fem gånger bättre än bästa alternativ.

För flera år sedan ställdes Carl Ingemarsson, då doktorand på Institutionen för systemteknik, inför utmaningen att snabba upp klockfrekvensen på en FFT. Om han fick upp den i över 450 MHz skulle han slippa det sista steget i en doktorandkurs, vilken var att simulera effektförbrukningen.

|

| Carl Ingemarsson |

− Det övertygade mig om att på djupet undersöka hur logiken representeras i en FPGA, säger Carl Ingemarsson, numera konsult på Ericsson där han arbetar med att bygga en testbädd för 5G-basstationer.

Hans djupdykning i FPGA-logiken betalade sig, den sista uppgiften i doktorandkursen ströks. Likaså blev den startskottet på ett forskningsrapport som tydligt visar att det går att öka beräkningshastigeten i en FPGA utan att det kostar mer hårdvara.

Hemligheten är att använda logiken så att den passar bättre till FFT:n.

|

| Oscar Gustafsson |

− De flesta försöker beskriva en uppgift så att så få grindar som möjligt går åt i någon tänkt asic-implementation. Vi har beskrivit logiken så att den utnyttjar FPGA:ns resurser till max, förklarar Oscar Gustafsson, docent vid Institutionen för systemteknik vid Linköpings universitet.

Direkt kan man konstatera att de allra flesta inte har en chans att nå det fantastiska resultat som forskarna visar upp i sin rapport. Här har främst Carl Ingemarsson funderat, vänt och vridit på designen för att pressa ut det yttersta.

Realiserad i två olika Xilinxkretsar – en Virtex4 och en Virtex6 – ger byggblocket mer än 350 procent ökad datatakt per resursenhet (slice) i FPGA:n. Den ökade beräkningseffektiviteten är en kombination av en högre klockfrekvens och att framförallt färre resurselement krävs. Då bör det tilläggas att detta är en jämförelse med det allra bästa som någon annan tidigare visats upp.

|

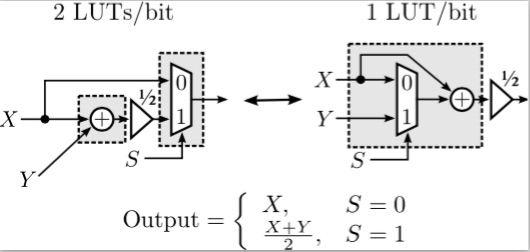

| Genom att skruva på detaljer i standard-metoder har forskarna utnyttjat FPGA-hårdvaran till det yttersta. Ett typexempel är att byta plats på addition och multiplexer. Normalt görs addition före en mux, vilket kräver två FPGA-resurser. Byter man plats på funktionerna går det däremot bara åt en FPGA-resurs. |

Runt hälften av förbättringarna som Linköpingsgruppen gjort bottnar i trix som är väldigt FFT-specifika och detaljrika. Den andra hälften är mer rätt fram.

− En design var jag tvungen att handplacera i FPGA:n eftersom verktyget vägrade att placera på det sättet som jag insåg skulle bli bättre, säger Carl Ingemarsson och han fortsätter:

− Annars handlar det bättre resultatet mest om att jag ändrat i min VHDL-kod, alltså att jag på en högre nivå ändrat logiken för att den ska mappa bättre mot FPGA:n.

Till stor del har alltså forskarna utgått från standardmetoder när de skapat sitt byggblock; en 1024 punkters FFT som räknar en sampel per klockcykel. Dessa har de modifierat för att passa bättre till hårdvaran.

Ett smart och enkelt sätt att utnyttja logiken bättre kan vara att byta ordningen på vissa standardmässiga operationer. Ett typexempel är en multiplexer som följer på en addition. Den designen tar två FPGA-resurser. Vänder man istället på det hela så går det att få in i en resurs.

Hur mycket en specifik konstruktion kan vinna på den metodik som de svenska forskarna arbetat fram är svårt att säga. Det beror på många saker, inte minst aktuell tillämpning och arkitektur.

Däremot ser forskarna inget hinder när processerna krymper så länge inte FPGA-tillverkarna ändrar strukturen på sina logikblock. För många typer av signalbehandling med höga prestanda går det att vinna mycket på deras metod.

− Arkitekturen i pappret tar in ett sampel per klockcykel. I andra arkitekturer kan man ta in flera sampel per klockcykel, men det går fortfarande att applicera det jag gjort i en sådan arkitektur, säger Carl Ingemarsson.

Denna artikel har tidigare publicerats i magasinet Elektroniktidningen. För dig som jobbar i den svenska elektronikbranschen är Elektroniktidningen gratis att prenumerera på – våra annonsörer betalar kostnaden. Denna artikel har tidigare publicerats i magasinet Elektroniktidningen. För dig som jobbar i den svenska elektronikbranschen är Elektroniktidningen gratis att prenumerera på – våra annonsörer betalar kostnaden.Här ansöker du om prenumeration (länk). |

En stor del av arbetat handlar om att skriva riktigt bra VHDL-kod. För det krävs att man verkligen förstå vad det ska bli för hårdvara i slutänden.

− En del av det jag gjort är väldigt specifikt för Xilinxs FPGA:er som jag jobbat med, men mycket kan användas betydligt bredare, säger Carl Ingemarsson.

Då syftar han på de mer generiska tricken som förvånansvärt nog företag som exempelvis Xilinx inte har tagit hänsyn till i sina kodgeneratorer idag.

− Konstruktionsprogramvaran som finns tillgänglig är ganska rätt fram men inte på något sätt optimerad för sin egen plattform. Dagens asic-verktyg gör exempelvis mycket mer magi, säger Oscar Gustafsson.

Och han fortsätter:

− Genom att vår ip-kärna mappar extremt bra till FPGA:n tar den mycket färre resurser än Xilinx egna FFT-block utan att vara långsammare.

En viktig detalj är just att Linköpingsforskarnas ip-kärna inte gör FFT:n på ett annorlunda sätt, utan den utnyttjar logiken som krävs för att göra FFT:n på ett betydligt med effektivt sätt än någon tidigare lyckats med.

Det har också legat dem i fatet. Det tog lång tid för bedömare inom forskningsvärlden att inse storheten i arbetet – de svenska forskarna använder sig ju av samma algoritm och samma arkitektur som alla andra.

− Vårt argument vara att trots att vi använder samma algoritm och samma arkitektur så tjänar vi extremt mycket. Vår ip-kärna är tre till fem gånger bättre än bästa alternativ och då har vi bara trollat med mappningen till FPGA:n, säger Oscar Gustafsson.

Nästa käpp i publiceringshjulet dök upp när rapporten skickats in. Då kom det fram att en annan forskare redan publicerat Linköpingsforskarnas lösning.

− Vår material kom i händerna på en utländsk forskare, som kopierade och publicerade det. Det tog ett år att reda ut, men nu är han som stal vårt material avstängd från publicering hos IEEE i fem år, berättar Oscar Gustafsson.

IEEE-artikel |

|

Artikeln ”Efficient FPGA Mapping of Pipeline SDF FFT Cores” är skriven av Carl Ingemarsson, Petter Källström, Fahad Qureshi och Oscar Gustafsson. Den publicerades på IEEE Xplore i juni och finns med i septemberupplagan av den månatliga journalen IEEE Transactions on Very Large Scale Integration (VLSI) Systems. Här kan du hitta den (länk). |

I somras blev resultatet äntligen publicerat av IEEE (se rutan till höger).

Vid sidan av sitt arbete på Ericsson försöker Carl Ingemarsson att få industrin intresserad av det fina resultatet.

− Jag har försökt få kontakt med Dillon Engineering som är en firma i USA som säljer FFT-ip, men ännu inte lyckats, säger Carl Ingemarsson.

− Jag har även haft lite diskussion med Xilinx som har ett tredjepartsleverantörsprogram, men det är svårt eftersom jag inte har en lite större firma i ryggen.

Forskargruppen på universitetet arbetar i nuläget med att få till en fortsättning, där fokus ligger på att optimera algoritmer för FPGA:er. För att komma vidare krävs fler kontakter med företag som är intresserade av signalbehandling med extremt hög prestanda.

− Vi har också tagit fram en ännu bättre variant av FFT:n, som utnyttjar ännu mindre logik. Men den är inte publicerad ännu, avslöjar Oscar Gustafsson.