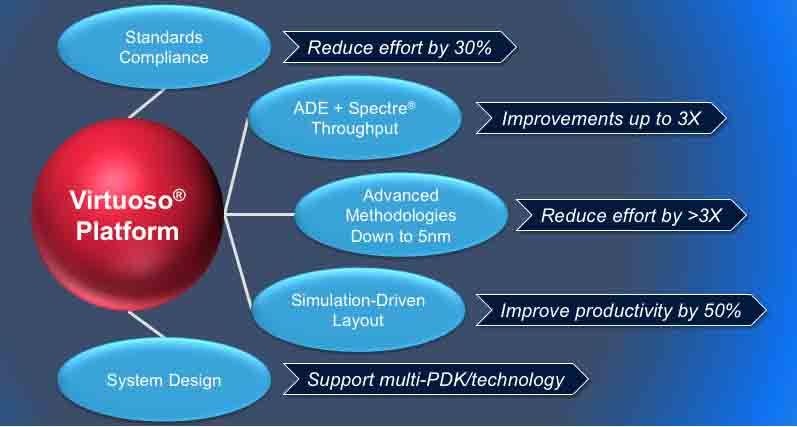

Virtuoso är EDA-jätten Cadence flaggskepp för konstruktion av analoga och blandat analog-digitala kretsar. Senaste versionen är mellan 30 och 300 procent bättre än föregångaren.

Virtuoso är EDA-jätten Cadence flaggskepp för konstruktion av analoga och blandat analog-digitala kretsar. Senaste versionen är mellan 30 och 300 procent bättre än föregångaren.

– Det finns tre viktiga teman i den nya releasen som alla är stora för mig och Cadence. Den första är systemdesignplattform som vi släppte förra året men som är förbättrad på alla punkter. Den andra är att vi stödjer 5 nm och den tredje är den simuleringsdrivna layouten, säger Yuval Shay på Cadence.

Som exempel på vad Virtuoso 18.1 klarar tar han en lidar där man förutom analoga och digitala kretsar också måste integrera mikromekaniska speglar och optokomponenter på bäraren plus att allt ska kapslas.

– Vi har haft en del av funktionerna sedan tidigare men nu kan man göra allt med Virtuoso, från schemat till SIP-lösningen plus att man kan göra EMC-analyser och se hur hela systemet fungerar.

En annan nyhet är att Virtuoso numera kan användas för att konstruera i 5 nm-processer. Det är inte helt lätt att definiera processnoder, men TSMC ska rampa upp vad företaget kallar en 7 nm-process i år och siktar på 2019 för 5 nm.

Den tredje förbättringen är den simuleringsdrivna layouten som kan öka produktiviteten med så mycket som 50 procent.