Tjeckiska Codasip har trimmat sin svit av 64-bitars Linux-cpu:er på Risc V – nu är de dual isssue. Företaget utvecklar IP-kärnor för integrering i systemkretsar.

Tjeckiska Codasip har trimmat sin svit av 64-bitars Linux-cpu:er på Risc V – nu är de dual isssue. Företaget utvecklar IP-kärnor för integrering i systemkretsar.

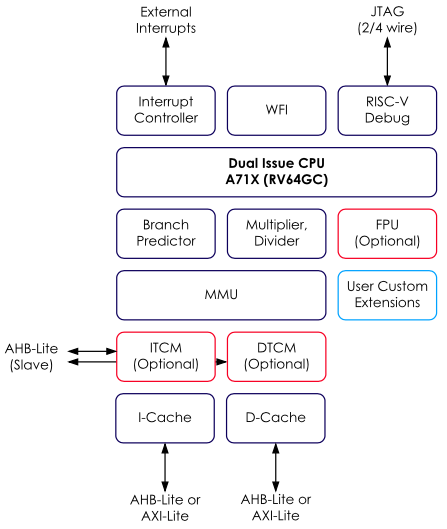

Codasip hade utlovat nya versioner med dessa egenskaper och säger nu att de kommer att finnas tillgängliga mot slutet av året. Det handlar om företagets vassaste familj av 64-bitarskärnor. De kan nu starta två instruktioner parallellt. De nya modellerna byter logiskt namn från A70X till A71X.

Att de kan starta två instruktioner parallellt betyder att de potentiellt kan exekvera fler än en instruktion per klockcykel – att de är ”superskalära”. Enligt Codasip gör dual issue-funktionen av med försumbart mycket chiparea.

A71X-sviten släpps som sina föregångare i varianter med två tillval: att kunna konfigureras till symmetriska fyrkärnor och/eller att stödja packade SIMD-instruktioner. De finns som förut också med både AHB- och AXI-gränssnitt.

De har flyttalsenhet och stöder atomära instruktioner. De har MMU och stöder machine-, supervisor- och user-rättighetshierarkin – det här är centralt för att de ska kunna köra ett fullvärdigt Linux.

De har flyttalsenhet och stöder atomära instruktioner. De har MMU och stöder machine-, supervisor- och user-rättighetshierarkin – det här är centralt för att de ska kunna köra ett fullvärdigt Linux.

Exempel på tillämpningsområden är artificiell intelligens och fordonsdatorer.

Vill du fintrimma Codasips egna konstruktioner, exempelvis genom att lägga till egna instruktioner, så har Codasip verktyg som låter dig göra detta. Det är samma verktyg som Codasip själv använder för att producera sina CodAL-modeller.

Codasip kallar sig för den ledande leverantören av konfigurerbara Risc V-kärnor. Enligt Elektroniktidningens anteckningar var företaget först att erbjuda kommersiella cpu-kärnor på den öppna gratisarkitekturen Risc V.

Risc V är en öppen och gratis instruktionsuppsättning skapad av ledande cpu-forskare och kommersialiserad med starkt stöd från industrin. Risc V utmanar de proprietära arkitekturerna Arm och x86 på samma sätt som Linux utmanar proprietär Unix och Windows.