För precis två år sedan tog FPGA-jätten Xilinx steget till 16 nm och avslöjade de första detaljerna kring Zynqfamiljen UltraScale+. Nu tar företaget ytterligare ett steg – de första FPGA:erna med integrerade AD- och DA-omvandlare som samplar i GHz-takt avsedda för bland annat antennära 5G-tillämpningar är redo för lansering.

För precis två år sedan tog FPGA-jätten Xilinx steget till 16 nm och avslöjade de första detaljerna kring Zynqfamiljen UltraScale+. Nu tar företaget ytterligare ett steg – de första FPGA:erna med integrerade AD- och DA-omvandlare som samplar i GHz-takt avsedda för bland annat antennära 5G-tillämpningar är redo för lansering.

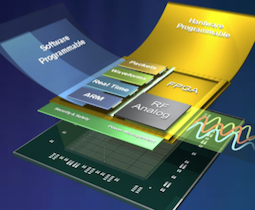

Zynq UltraScale+ MPSoC är namnet på Zynqfamiljen tillverkad i TSMC:s 16 nm FinFET-process. Enligt företaget passar den tredimensionella processen väl för analoga funktioner, vilket ligger bakom att Xilinx nu lanserar RFSoC, ”radio frequency system on a chip” som innebär att företaget integrerat riktigt snabba dataomvandlare direkt på chipet.

Vid introduktion pekar företaget på att den vässade arkitekturen i ett första skede siktar på en plats i utbrutna radioenheter (remote radio head, RHH) med multipla kanaler och mobilt backhaul, även om den på sikt kommer att kunna användas i basbandet. Det handlar om antennära massiv Mimo-lösningar där utrymme och värmutveckling är två kritiska parametrar.

I stort kan Xilinx tekniklansering delas upp i tre delar: på chipet kan 12 bitars AD-omvandlare som samplar med upp till 4 GSa/s liksom 14-bitars DA-omvandlare som samplar med upp till 6,4 GSa/s integreras. Likaså används direktsampling på ingången, vilket betyder att man inte blandar ner den analoga insignalen i flera frekvenssteg.

Hittills har testchips tagits fram, medan produktlanseringar kommer senare.

– De första riktiga produkterna släpper vi senare i år. Då kommer vi att berätta mer detaljer om dataomvandlarnas prestanda i form av dynamik, signal-brusförhållande och annat, säger Kirk Saban, produktansvarig för FPGA och SoC på Xilinx till Elektroniktidningen.

Så länge det inte finns konkreta kretsar att tala om är det svårt att jämföra konstruktionen prestandamässigt med alternativa lösningar.

På en direkt frågan om hur många antennelement ett enstaka chip i framtiden kommer att kunna stödja svarar Kirk Saban:

– Det beror på vilket frekvensband du vill stödja. Men vi kan klara sub 6GHz-radio och stödja en 8 x 8 antennmatris med ett chip. Vid lägre datahastighet kommer vi även att kunna stödja 16 x 16 matriser.

När företaget plockar in dataomvandlarna på det digitala chipet skippar det också det plats- och energislukande seriella höghastighetsgränssnittet baserat på JESD204B-protokollet.

– Vår lösning gör att ett stort antal externa AD- och DA-omvandlare kan tas bort. Därmed eliminerar JESD204B-gränsnittet i både de externa kretsarna och på vårt chip. Det ger en radikalt minskad effektförbrukning liksom ett betydligt mindre fotavtryck jämfört med diskreta lösningar.

Ytterligare en finess som Xilinx lyfter fram är direktsampling. Det är inget nytt, men kräver att den samplade signalen snyggas till genom avancerade filtreringstekniker i den digitala domänen. Något Xilinx hanterar direkt på chipet.

– Beroende på konstruktionen, antal dataomvandlare och datahastighet som används, kommer vår lösning att kunna minska effektförbrukningen i den digitala delen av radion med mellan 40 och 50 procent, säger Kirk Saban.

På samma sätt talar företaget om att storleken på en framtida konstruktion kan minska med 50 till 70 procent genom att diskreta dataomvandlare inte längre krävs.

Man ska dock ha i åtanke att alla jämförelser är baserade på att AD- och DA-omvandlare som används är enkla. Idag finns, och framåt kommer fler, gigabitsamplande dataomvandlare i dual- och quad-format.

Nedan, illustraton över Xilinx tillvägagångsätt: