Processorer, system-IP och minnes-IP finns i en Arm-baserad systemchiplet från Cadence. Den har just gått till tape-out.

Processorer, system-IP och minnes-IP finns i en Arm-baserad systemchiplet från Cadence. Den har just gått till tape-out.

Chipletten är en prototyp som demonstrerar Cadence verktygskedja för chiplets – Cadence Chiplet Architecture and Framework. Arm har varit partner i att förenkla konstruktionsprocesserna och trimma prestanda.

Ytterligare två avdelningar på Cadence ska ha credit för projektet: Cadence Design Services och Cadence Silicon Solutions Group.

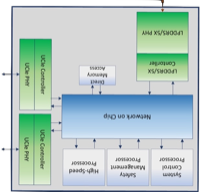

Cadence chiplet innehåller en systemprocessor, en säkerhetsprocessor, en kontroller, PHY-IP för LPDDR5 och UCIE, samt Janus – Cadence teknik för nätverk-på-chip (NoC). Cadences UCIE-IP har upp till 64 Gbyte/s toppbandbredd och dess LPDDR5-IP har upp till 32 GB/s.

Grundtanken med chiplets är återanvändning – att ett och samma chiplet skunna användas i fler olika produkter. Du ska exempelvis kunna blanda chiplets tillverkade i olika processnoder

Cadence chiplet följer standarderna UCIE (Universal Chiplet Interconnect Express) och CSA (Arm Chiplet System Architecture). UCIE är som PCIE, men på chipnivå. Chiplettarna kopplas samman med varandra via mellanliggande kiselskivor (interposers) eller genomgående hål (thru silicon vias).

En av tankarna bakom att dela upp stora monolitiska chips i mindre sammanfogande chiplets är att korta utveckliingstiden. Särskilt pekar Cadence på datacenter, högprestandaberäkningar och fordon.