Precis som konkurrenten Altera pystar Xilinx ut information om sin kommande generation FPGA:er med jämna mellanrum. Redan i januari fick vi veta att designverktyget Vivado skulle få stöd för den nya generationen i mars och att tape out skulle ske under andra kvartalet (länk).

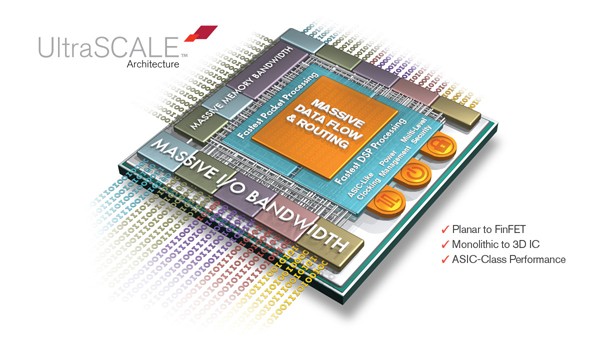

Några dagar för sent, 9 juli, kom pressmeddelandet som berättade att konstruktionsarbetet var klart. Vi får dock vänta på de första samplen till fjärde kvartalet och Xilinx berättar inte särskilt mycket om hur den nya arkitekturen som kallas UltraScale kommer att se ut.

Ett problem med stora FPGA:er är att kommunikationen lätt blir en flaskhals. Det handlar både om att skyffla data från och till omvärlden men också internt på FPGA:an, något som i praktiken innebär att man aldrig kan nyttja logiken till hundra procent.

Designverktyget Vivado är förbättrat så att man med UltraScale ska komma över 90 procents nyttjandegrad utan att tappa prestanda. Vivado tar hela konstruktionen och testar olika topologier för att se vad som fungerar bäst.

Xilinx har också gjort om klockdistributionen så att är mer asicliknande med olika klockor i olika områden. Uppdelningen är dessutom finkornigare än tidigare och därmed ska man slippa problem med långa distributionsavstånd som kan ge upphov till förskjutningar (skew).

Andra nyheter är att multiplikatorerna i DSP-blocken är bredare och att det finns fler och sanbbare IP-block för externa DRAM-minnen.

Men vi får vänta ytterligare några månader innan vi vet exakt hur kretsarna i den nya UltraScale-arkitekturen ser ut.