Staplat DRAM standardiseras

Staplat DRAM standardiseras

Ett första utkast till en standard har släppts för Samsungs och Microns nya minnestyp Hybrid Memory Cube (HMC), en teknik som lovar 15 gånger högre datatakt än DDR3 och 70 procent mindre energiförbrukning per bit i första generationens kretsar. Utkastet beskriver det fysiska gränssnittet och protokoll för anslutningar på korta avstånd. Några lämpliga tillämpningsområden för den här varianten är snabba nätverk, industri och test och mät.

I nästa steg ska standardgruppen ta fram gränssnitt för extremt korta avstånd – under tre tum – för anslutning av minnet till FPGA:er, asicar och ASSP:er. Hela standarden ska vara spikad innan årsslutet.

Att HMC-tekniken var på väg till tillverkning annonserades i höstas.

IBM kommer att tillverka minnet i 32 nm high-K metal gate, med hjälp av sin 3D-tillverkningsteknik med viahål. Enligt tidningen EE Times har det tidigare annonserats att de första minneskretsarna kommer att dyka upp år 2013 i storlekarna 2 och 4 Gbyte.

Altera kommer att koppla HMC-minnen till sina 28 nm-FPGA:er. Xilinx antyder samma intresse. IBM antyder ett intresse för att använda tekniken i servrar.

Övriga medlemmar av standardgruppen är ARM, HP, Microsoft, SK Hynix och Open-Silicon. Ytterligare 155 företag har enligt Micron meddelat att de är nyfikna på tekniken.

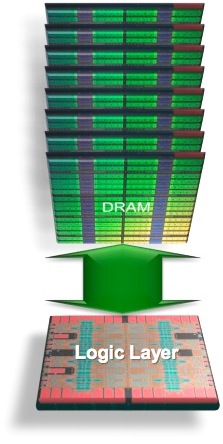

Minneskretsarna byggs genom att chipsen staplas på varandra. Ett chip i botten innehåller all minneslogik, för bland annat refresh och felkorrigering. Minneschipsen förbinds med logikchipet vertikalt med tusentals kopparpelare som står i schakt genom kislet (TSV, Thru Silicon Via), utom det understa chipet som ligger ansikte mot ansikte med logikchipet.

Första generationen ska ha en bandbredd på 128 Gbyte/s. Den använder fyra staplade minneschips. Generation fem ska enligt planen ha en bandbredd på 1024 Gbyte/s.

Effekten hos minneskretsen ska hållas under 15 watt över generationerna, vilket betyder att energin per bit måste sänkas, från 20 pJ i första generationen till 4 pJ i generation fem, är planen.

På sikt ska HMC-minnen användas också i konsumentelektronik.

Gränssnittet mellan minne och logik följer Jedecstandarden JESD229. Fler detaljer om hur HMC kan komma att tillverkas finns här (länk).