Tabula: observera designen i realtid

Tabula: observera designen i realtid

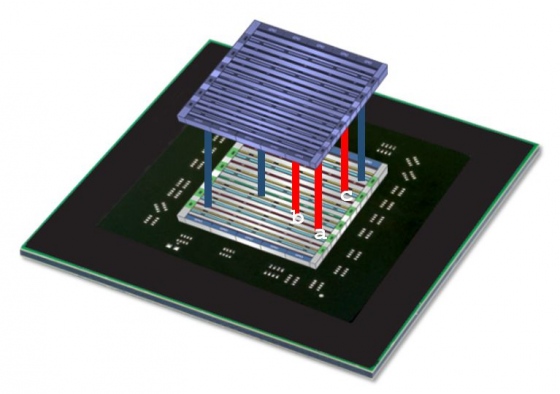

Att verifiera en stor och komplex konstruktion kan stå för så mycket som 70 procent av utvecklingskostnaden. FPGA-uppstickaren Tabula har en helt ny lösning kallad DesignInsights som är inbyggd i arkitekturen och som stöds av utvecklingsverktyget Stylus 3.0.Tabula använder samma SRAM-baserade arkitektur som Xilinx och Altera i Abax-familjen men har ett unikt sätt att koppla ihop uppslagstabellerna, LUT:arna. Tekniken kallas Spacetime och företaget beskriver den som att uppslagstabellerna förutom att ha förbindelse med sina grannar som ligger i samma plan även har kontakt med den uppslagstabell som finns ovanför och med den som finns under. Dessutom går det att spara åtta olika varianter av innehållet på uppslagstabellernas in- och utgångar.

I och med att det övre lagret hela tiden ”ser” innehåller på alla de aktiva uppslagstabellernas utgångar kan det plocka upp värdena. Det går också att använda värdena för att skapa 128-bitars triggvillkor.

Tekniken kräver ingen extra logik förutom ett litet buffertminne på 1,3 Mbit där de maximalt 256 signaler man kan studera lagras. Den som vill ha mer minne, och vars konstruktion inte fyllt upp arbetsminnet, kan använda även den lediga delen av arbetsminnet som buffertminne.

Själva utläsningen av signalerna kan ske i ett betydligt lägre tempo än insamlandet som går lika snabbt som kretsen klockas. För Abax2 kan det ske med 2 GHz.

Eftersom funktionen är inbyggd i kretsarna och konfigureras med det molnbaserade utvecklingsverktyget Stylus 3.0 och System Verilog så fungerar den lika bra i labbet som när kretsen hamnat i en produkt och placerats ut hos en slutkund.