Intels mjuka processorkärna Nios II får nu sällskap av Nios V, företagets implementation av öppenkodsprocessorn Risc-V.

Nios är en familj av små, konfigurerbara processorkärnor som körs i FPGA:ernas logikblock och hanterar enklare uppgifter. Intel har sedan länge den egenutvecklade 32-bitarskärnnan Nios II och nu adderas alltså en implementation av Risc-V.

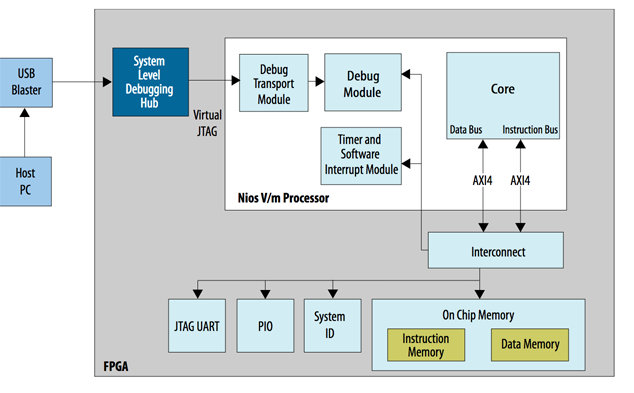

Det handlar om instruktionsuppsättningen RV32IA med en femstegspipeline och en AXI4-buss för kommunikation med andra block på kretsen.

Implementationen fungerar på FPGA-familjerna Cyclone10, Arria 10, Stratix 10 och Agilex.

Nios V kommer med utvecklingsverktyget Quartus Prime Pro Edition Software i version 21.3 eller senare.