En nybildad arbetsgrupp under ledning av en FPGA-legendar ska försöka standardisera hur extrainstruktioner adderas till Risc V för att skapa en grund för ett smidigt ekosystem för acceleratorer.

|

| Det utvecklas en standard för hur Risc V-kärnor ska kopplas till acceleratorkärnor. |

Många lockas till Risc V för tryggheten i att ha en komplett mjukvarumiljö med kompilatorer och operativsystem, samtidigt som möjligheten finns att utöka instruktionsuppsättningen med hårdvaruaccelererade specialinstruktioner för att passa specifika behov.

Men fram till idag har det saknats en gemensam standard för hur dessa acceleratorer ska användas tillsammans med en processor, och framför allt hur de ska återanvändas.

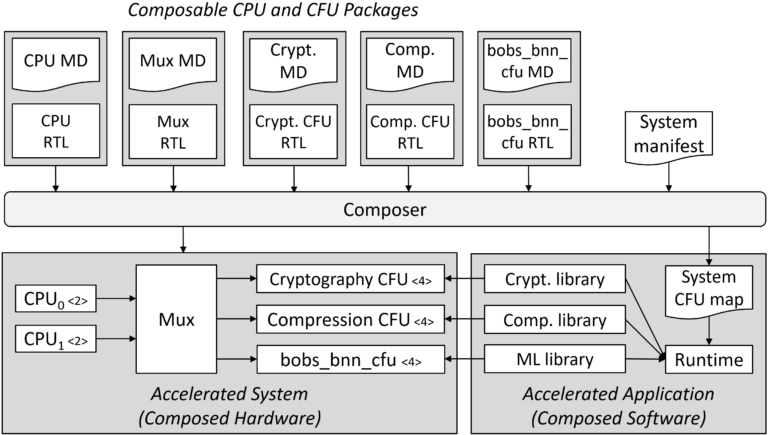

En arbetsgrupp under ledning av FPGA-legendaren Jan Gray har nu tagit fram en specifikation för att enkelt ansluta CFU (Custom Function Units) till en Risc V-processor. Ambitionen är att skapa ett ekosystem av återanvändbara acceleratorer för allt från kryptografi och maskininlärning till datakompression.

Specifikationen håller just nu på att klubbas och kommer även att presenteras på RISC-V Week i Paris i början av maj.