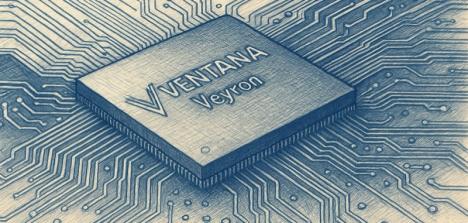

I senaste versionen av sitt syntesverktyg utnyttjar Synopsys data från halvledarprocesserna för att redan från RTL-nivå bättre förutse timing och kiselyta i den färdiga kretsen. Resultatet är utdata med högre kvalitet, vilket ökar verktygets trovärdighet och konstruktörernas produktivitet.

Nio gånger noggrannare timing och sex gånger noggrannare ytuppskattningar - det är vad Synopsys hävdar att den nya versionen av det klassiska syntesverktyget Design Compiler klarar. Det innebär att timingen i kretsen bara avviker med högst fyra procent från den timing verktyget förutspår. Och ytan med bara någon procent.

Verktyget, världens mest använda syntesprogram vars första version kom redan 1988, når de resultaten tack vare en ny modelleringsmetod kallad "topografisk teknik" (topographical technology). Den ersätter de tidigare använda modellerna som bygger på laster i ledningarna (wire load models).

Istället för lastberäkningar utnyttjar verktyget information från halvledarprocessen, extraherade ur samma databas som används för Synopsys fysiska syntesverktyg IC Compiler. Arbetssättet går ut på att göra en virtuell layout som uppdateras i takt med att syntesen fortskrider. Data om timing och yta, liksom strömförbrukning och test, hämtas successivt från databasen. Det handlar inte om någon komplett placering och ledningsdragning utan mer om att ta ett nät i taget, göra en tentativ layout och se till att kraven på timing, yta och effekt uppfylls. Skulle något krav brytas mot så river verktyget upp en del av jobbet och gör en ny virtuell layout.

Samma verktygsflöde

Synopsys poängterar att det inte blir någon skillnad i konstruktionsflödet. Under förutsättning att verktygen lyckas möta kraven blir utdata, precis som tidigare, en nätlista - alltså underlag för kretslayout. Skillnaden är bara, enligt Synopsys, att yta och timing för denna nätlista ligger betydligt närmare den slutliga kretsen än äldre nätlistor.

Synopsys har låtit ett antal nyckelkunder prova verktyget, och flera av dem hävdar att såväl produktivitet som förutsägbarhet ligger i linje med vad Synopsys hävdar.

Verktyget ska finnas tillgängligt för leverans i september. Det utgör den tredje och sista pusselbiten i Synopsys konstruktionsplattform Galaxy, där även IC Compiler för fysisk syntes och verktyget Signoff för avlämning till halvledarproducenten.

Påpekas bör att Design Compiler gick igenom en rejäl uppfräschning redan förra året. Då infördes effektoptimering och testvektorkompression. Dessutom dubblerades såväl hastigheten som kapaciteten.

Adam Edström