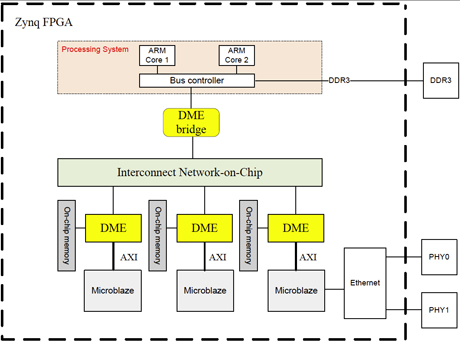

AXI är Arms buss för kommunikation mellan processorkärnorna och andra IP-block på kretsen. Den används i både Xilinx och Alteras systemkretsar, det vill säga Zynq respektive Cyclone SoC.

Problemet med minnesaccessen växer snabbt med antalet processorkärnor och IP-block som behöver tillgång till minnet.

– Har du bara de två Armkärnorna är det ingen vits att använda DME. Vi kommer till vår rätt när det är en fem, sex kärnor eller mer.

Elsips IP-block är osynligt för programvaran trots att det tar hand om minneshanteringen.

– Dessutom är det skalbart så det hänger med när man ökar antalet processorer.

I Zynqversionen har Elsips DME (Data Management Engine) fått sällskap av två nya IP-block. Det är ett Network-on-chip (NoC) och en modifierad variant av DME:n som mer liknar en brygga. Den senare hjälper de två Arm-kärnorna att sköta minneshanteringen medan DME:n är parhäst Xilinx mjuka processor Microblaze. Allt kopplas ihop via NoC:en.

Har man andra IP-block i FPGA-delen som också behöver tillgång till minnet, kan de antingen få en egna DME-block eller så kan de gå via en Microblazekärna.

Minnet kan delas upp i olika block som kan vara gemensamt för flera processorer vare sig det är internt i kretsen eller externt. Men det går också att reservera delar av minnet för en specifik processorkärna.

– Vi har utvecklat tekniken i samarbete med en kinesisk kund men vi säljer den som en standardprodukt, säger Adam Edström.

Elsip överväger att anpassa tekniken så att den fungerar även med Cyclone SoC från Altera.

Företaget knoppades av från KTH år 2011 och bygger på forskning av Axel Jantsch, Ahmed Hemani och Zhonghai Lu.