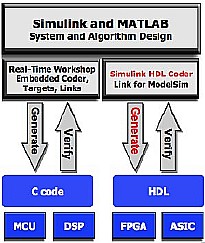

Nu säger dock The Mathworks att man täppt till detta hålrum. Nylanserade Simulink HDL Coder tar den exekverbara Simulinkmodell som konstruktören utvecklat, och ger snabbt och automatiskt VHDL eller Verilogkod för såväl dataflöden som tillståndsmaskiner. Koden kan användas till såväl asicar via syntesprogram som Design Compiler eller till FPGA:er via Xilinx eller Alteras egna program.

– Den stora poängen är att både hårdvara och programvara kan genereras från samma Simulinkmodell, säger Sudhir Sharma, produktansvarig på The Mathworks.

Samtidigt genereras en testbänk, även det helt automatiskt. Tidigare har HDL-kodningen av såväl själva konstruktionen som testbänkarna fått göras manuellt. Testbänken kan användas med stimuli från verkligheten och utdata från testerna kan ses på oscilloskop, logikanalysator eller annat lämpligt instrument.

HDL-koden blir funktionellt ekvivalent med Simulinkmodellen, alltså både bitriktig och cykelriktig. Modellerna kan även inbegripa befintliga IP-block. Gränssnitt för dessa genereras också automatiskt av verktyget.

Såväl VHDL- som Verilogkoden följer den senaste versionen av respektive standard. Dock uppfylls ännu inte hela standarderna – för datavägar finns ett 80-tal block i Simulink som stöds, och styrlogiken är begränsad till de tillståndsmaskiner av Mealy- och Moore-typ som stöds av företagets verktyg Stateflow.

Att detta är en första version av verktyget märks också på optimeringsmöjligheterna som är ganska måttliga. Användaren kan visserligen välja mellan HDL-kod optimerad för yta, effektsnålhet eller hastighet genom att styra vad som ska implementeras seriellt och parallellt. Men för att se hur resultatet blev i dessa avseenden så måste konstruktionen först syntetiseras, och återkopplingen från grindnivå upp till Simulinknivå är alltjämt ett ingenjörsintensivt arbete.