På mässan DAC i nästa vecka visar Hardi Electronics hur höghastighetslänkar av typen Serdes kan konstrueras in i asicar och hur konstruktionen verifieras. Lösningen är utvecklad tillsammans med LSI Logic.

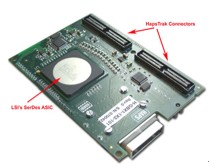

På mässan DAC i nästa vecka visar Hardi Electronics hur höghastighetslänkar av typen Serdes kan konstrueras in i asicar och hur konstruktionen verifieras. Lösningen är utvecklad tillsammans med LSI Logic.Produkten som samarbetet resulterat i är också intressant - en utökning av Hardis prototypsystem Haps med ett dotterkort som klarar seriella höghastighetstransceivrar av Serdes-typ. Nykomlingen, som stöder PCI Express, SAS, Sata, Fibre Channel, Infiniband och Gigabit Ethernet, ska visas upp i San Diego i nästa vecka, på mässan DAC, Design Automation Conference.

- Allt fler kunder får stora problem med höghastighetsgränssnitt i sina asicprototyper. Vi är jätteglada över att få jobba med LSI för att lösa dessa problem, säger Hardis vd Lars-Eric Lundgren i ett pressmeddelande.

Hardi konstaterar att möjligheterna är klart begränsade för den som vill göra en Serdesprototyp i en FPGA. Den beter sig annorlunda än en asic såväl logiskt som elektriskt, och RTL-koden som verifieras i prototypen måste ta hänsyn till skillnaderna i funktionalitet. Att därför använda en "riktigt" asic-serdes för prototyperna är därför ett bättre alternativ, resonerar företaget.

Dotterkortet är förstås direkt anslutbart till Hardis prototypkort och klarar lika höga krav. Användaren behöver inte bry sig om signalintegritet, strömförsörjning, jordning eller andra frågor som har med kretskortslayout att göra - allt sådant är löst av Hardi och LSI.