Mips första egna 64-bitare

Mips första egna 64-bitare

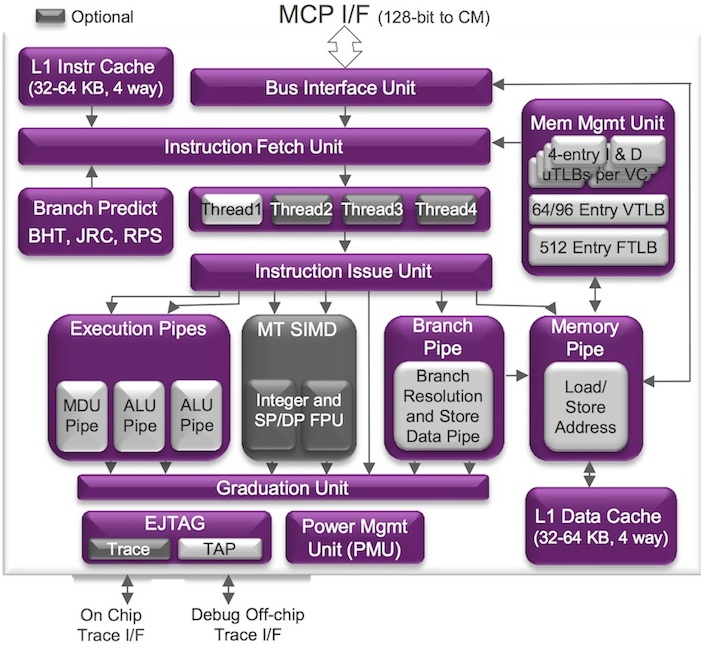

64-bitars MIPS-kärnor har konstruerats drygt tjugo år. Men detta är första gången arkitekturens ägare släpper en egen konstruktion. Warrior I6400 heter den. Den är multitrådad, har hårdvarustöd för virtualisering, och kan användas i multikärnor och koherenta kluster. – Vi hade tur med timingen. Vi har jobbat med den i några år och nu släpper vi den precis när flera marknader håller på att gå över till 64 bitar, säger Mark Throndson, ansvarig för marknadsföringen av Imaginations processorkärnor.

| |

De konkurrerande arkitekturerna ARM och x86 har större ekosystem. Men Imagination budskap är att en stor trend just nu är vad som kallas ”instruction set neutrality” – att tillämpningar utvecklas för virtuella maskiner och portabla plattformar.

– Därmed kan arkitekturerna tävla på sina egna meriter. Mjukvaruutvecklarna är inte låsta till en viss instruktionsuppsätting, säger Mark Throndson.

Imagination hävdar att dess kärnor ger samma prestanda på mindre kiselyta – eller mer prestanda på samma – än konkurrenterna. I6400 ska enligt företaget ha över 50 procent högre prestanda i Coremark och 30 procent högre i DMIPS än ”ledande konkurrenter i samma klass”. Den har flyttalsenhet och 128-bitars SIMD-operationer med stöd för 64-bitars heltal och 64-bitars flyttal.

Företaget anser sig nu med sina olika cpu-kärnor ha täckt in alla tillämpningsområden från styrkretsar till 64-bitarsservrar, med de kärnor som redan fanns i sortimentet när Imagination köpte MIPS i slutet av 2012 och de kärnor företaget släppt sedan dess.

Warrior I6400 är den första MIPS-processor som använder MIPS Release 6. Den innehåller nya instruktioner som enligt Imagination ska öka prestandan för LLVM, JIT, Javascript, webbläsare och den adressoberoende maskinkod (PIC) som används i operativsystemet Android – nästa generation av Android kallad ”L” stöder 64-bitars MIPS.

I6400 har hårdvarustöd för fyra SMT-trådar. Multitrådning innebär att instruktioner från flera olika programtrådar kan exekveras under samma klockcykel. Den kan köra upp till 15 operativsystem som så kallade gäster under sig. Även de tidigare 32-bitars Warriorkärnorna har haft hårdvarustöd för virtualisering.

Ett cachekoherent kluster kan innehålla upp till sex kärnor. Upp till 64 kluster kan konfigureras. Heterogena kluster stöds, för framtida systemkretsar med CPU:er, GPU:er och andra kärnor.

Power gearing heter en energisparteknik som används i I6400. Varje kärna kan ha sin egen klockfrekvens och spänningsnivå även i cachekoherenta system.

I6400 har stöd för datasäkerhet i form av domäner som kan definieras och mellan vilka information inte ska kunna läcka över, för att man exempelvis ska kunna köra betalning och legitimering och andra datasäkerhetskritiska tillämpningar tillsammans med öppna tillämpningar på en och samma cpu-kärna samtidigt.

Öppenkodsprojektet Prpl stöder MIPS64 i emulatorn Qemu.

Kärnan ska finnas allmänt tillgänglig i december. Flera licenspartners har redan fått lägga händerna på den.

Ett par företag som redan tillverkar framgångsrika MIPS64-processor är Broadcom och Cavium.