Verifiering i UVM blev just mer användbar i och med att Verilator fick stöd för dynamisk schemaläggning.

Verifiering i UVM blev just mer användbar i och med att Verilator fick stöd för dynamisk schemaläggning.

Det finns idag ett antal verifieringsramverk som tillåter användarna att skriva sina tester i allt från C++ till Python. Men för den som helst håller sig till Verilog och kanske dessutom har en inarbetad UVM-miljö så finns förbättringsmöjligheter även här.

UVM är i dagsläget det mest populära ramverket för verifiering av digital logik. Det är i sig öppen källkod men kräver en proprietär simulator eftersom ingen öppen simulator har haft tillräckligt med stöd för System Verilog.

UVM är i dagsläget det mest populära ramverket för verifiering av digital logik. Det är i sig öppen källkod men kräver en proprietär simulator eftersom ingen öppen simulator har haft tillräckligt med stöd för System Verilog.

Det har funnits stort intresse från industrin att kunna använda Verilator, världens snabbaste Verilogsimulator som dessutom är öppen källkod, tillsammans med UVM.

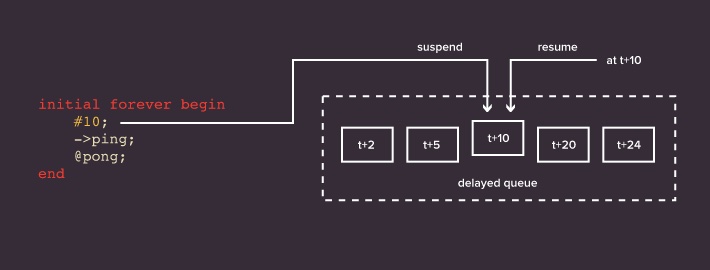

Tidigare har Verilator bara hanterat helt klocksynkrona händelser men nyligen togs ett stort kliv i den riktningen när stöd för dynamisk schemaläggning lades till för att stödja simulerade fördröjningar av signaler och asynkrona händelser.