Ett experiment i Lunds nanolabb hösten 2015 kan göra litografiprocessen i halvledarfabrikerna både billigare och energisnålare. Uppstartsföretaget Alixlabs har patenterat tekniken och siktar på att bli en del av den kommande 2 nm-noden.

Ett experiment i Lunds nanolabb hösten 2015 kan göra litografiprocessen i halvledarfabrikerna både billigare och energisnålare. Uppstartsföretaget Alixlabs har patenterat tekniken och siktar på att bli en del av den kommande 2 nm-noden.

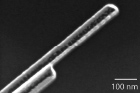

Uppdraget var utmanande men rättframt: tillverka nanotrådar som är mindre än 100 nanometer i diameter. Det var en del av Sabbir Khans examensarbete med Jonas Sundqvist och Dmitry Suyatin som handledare. Resultatet liknade dock mest urholkade trädstammar.

– Från början var 100 nm litet, men nu är det stort. Man ville ha ner diametern till 20 nm, säger Jonas Sundqvist, vd på Alixlabs.

I experimentet användes så kallad ALE, atomic layer etching, en torretsteknik som Jonas arbetat med på Infineon, sedermera Qimonda, och på Fraunhofer i Dresden. Vid upptäckten var han chef för Nanolabbet i Lund.

– När trådarna kom ut såg de ut som stenålderkanoter, en trädstam som man hackat ut i mitten. Vi satt och funderade några veckor på vad som hänt tills vi kom på att det var fantastiskt!

– När trådarna kom ut såg de ut som stenålderkanoter, en trädstam som man hackat ut i mitten. Vi satt och funderade några veckor på vad som hänt tills vi kom på att det var fantastiskt!

För att förstå storheten måste man ta sig ner till det understa lagret i halvledarkretsarna, till transistorerna. Där hittar man också de minsta geometrierna. Från 5 nm-noden används EUV, extremt ultraviolett ljus, med en våglängd på 13,5 nm för att göra litografin. I äldre processer är det istället immersionslitografi med en våglängd på 193 nm eller längre som används.

För att kunna skapa mönster som är mindre än ljuskällans våglängd har man från 28 nm tagit till knep som double patterning. Precis som namnet antyder görs två exponeringar med två olika masker för att skapa ett lager i kretsen.

Intel har tagit tekniken ett steg längre, för 10 nm-processen använder företaget fyra masker.

– Hade man inte fått EUV att fungera hade man fått gå till åtta masker per lager.

Förutom att tekniken ökar tidsåtgången och kostnaden så stiger även energiförbrukningen brant.

Det Jonas Sundqvist och hans kollegor kom på vid det misslyckade experimentet i Lund var att tekniken de testat på nanotrådarna gick att använda på fenan i FinFET-transistorerna, den gick att klyva på mitten med etsprocessen.

Det sker genom att omväxlande utsätta wafern för ett argonplasma för att aktivera ytan och sedan skicka in klorgas som den reagerar med.

– Man etsar bort ett atomlager per cykel. Sen håller vi på så här och varje gång tar vi bort två Ångström. Vi äter oss ned i kislet.

Etsningen sker bara där argonplasmat kommer i kontakt med ytan, vilket bestäms av masken. All övrig yta är opåverkad.

Dessutom ger etsningen kanter som är raka i vertikal led, de ligger mellan 80 och 90 grader.

Resultatet blir att fenan delas i två stycken parallella.

– Istället för att göra två exponeringar med EUV, en dubbelexponering, räcker det med en för att nå samma mål. Enkelt uttryckt kan man säga att vi från 14 nm kan göra 7 nm.

Även om det är en förenkling – det finns många varianter på hur litografin görs – visar det på potentialen.

Vet man dessutom att TSMC står för fem procent av hela Taiwans elkonsumtion idag och att företaget kan ha hundra EUV-maskiner om tre år är det lätt att inse att även energiaspekten är högintressant. Där har processen potential att spara mellan 25 och 50 procent i och med att man kan eliminera runt sju exponeringar.

Tekniken är patenterad i USA och Taiwan och en EU-ansökan är under behandling.

Nu i juni har företaget bokat in sig för att testa processen hos Plasway i Dresden.

– De bygger avancerad plasmaetsutrustning för 300 mm. Vi ska föra över labbresultat till dem, säger Jonas Sundqvist.

Försöken i Lund gjordes på miniwafers som inte är mer än 10 mm i diameter.

Processen har också testats hos IBM i New York med wafers på 200 mm. Resultatet var lyckat och är publicerat.

Nästa steg blir att få in lösningen i en forskningsfabrik med 300 mm-skivor. Alternativen kokar ned till Fraunhofer i Dresden, Imec i Leuwen eller forskningsfabriken i Albany utanför New York om man inte vill åka till Asien.

Därefter går det att demonstrera tekniken för de stora drakarna som TSMC, Intel och Samsung.

– De måste kunna komma dit, processa och sedan gå tillbaka. Det vi ska göra nu är en engångsgrej där vi förstör skivorna genom att såga upp dem för att mäta.

Om allt faller väl ut skulle Alixlabs teknik kunna finnas i kommersiella processor om fem år.

– Den första möjligheten vi tittar på är 2 nm, säger Jonas Sundqvist.

Då introduceras en helt ny typ av transistor, en så kallad gate all around.

– Man kan se det som en evolution av FinFET. Man går ner till en fena som man sedan omvandlar till tre nanotrådar.

Processteget görs utan litografi genom att man etsar tvärs genom fenan vilket skapar de tre trådarna som sedan utgör source och drain.

TSMC håller på att bygga en fabrik i Hsichu, Taiwan, för 2 nm. Den ska rampas upp nästa år men om det blir med 5 nm eller 3 nm är inte klart. Bägge dessa baseras på FinFET-transistorer.

Men det finns inget som hindrar att tekniken även används i andra noder där man kör double eller quadrouple patterning.

Hittills har företaget klarat sig med minimal finansiering men i dagarna fick företaget klartecken till ett Vinnovaprojekt på en miljon kronor för att verifiera tekniken. Dessutom håller företaget på att ta in en första runda av riskkapital vilket ska räcka till slutet av nästa år när det är dags för nästa runda.

– Parallellt för vi diskussioner med en massa företag i branschen. Det kan gå snabbt, det finns lyckade exempel som Nanexa i Uppsala.

Företaget sysslar med ALD, (enkelt beskrivet är det ALE fast baklänges) men för att framställa nanobaserade läkemedel och Applied Materials riskkapitalbolag har investerat i företaget.

– Vi tittar mycket på dem, att det är möjligt att gå från startup och sluta avtal med de största om man har avancerad teknik.

Artikeln är tidigare publicerad i magasinet Elektroniktidningen. Artikeln är tidigare publicerad i magasinet Elektroniktidningen.Prenumerera kostnadsfritt! |

En skillnad gentemot Nanexa som gör det enklare för Alixlabs är att företaget inte ska bygga någon egen fabrik eller utveckla egna maskiner. Det handlar ”bara” om att licensiera tekniken.

– Vi lämnar över till andra som måste göra grovjobbet.

Inte en konkurrent till ASMLDen initiala reaktionen hos många är Lundabolaget utmanar den nederländska litografijätten ASML, men så är det inte. Alixlabs metod gör struktureringen vilket minskar kravet på litografiprocessen.

– Man kan köra immersionlitografi med double patterning och sedan lägga in vår metod eller börja med vår metod och sedan köra double patterning, säger Jonas Sundqvist. Detsamma gäller för EUV. – Vilken ordning man väljer beror på designen. Vi jobbar mest med att göra själva fenan i FinFET-transistorn. Det behövs EUV för att skapa mönstret i ungefär 25 av de understa lagen i processer på 5 nm eller mindre. I praktiken handlar det om transistorerna och de fyra understa ledarlagren som kopplar ihop dem. Högre upp i stacken är kopparledarna så grova att de kan göras med enklare litografimaskiner. – Double patterning är bra på linjemönster. Sen går man in med EUV och gör så kallad cut, delar linjen för att koppla ihop transistorerna enligt designen. En joker i leken är det som kallas Direct Self Assembly, DSA. Det är en alternativ lösning till Alixlabs metod som utvecklas av ett konsortium där bland annat Imec och Lund Nanolab ingår. – Det finns presentationer från Imec att de kan göra testwafers i deras linje men det har aldrig testats i produktion, så det finns ett antal frågetecken om den kommer att lyckas. Dessutom kan det bli så att Direct Self Assembly och Alixlabs metod blir komplementära, att de passar bäst för olika lager i halvledarstacken. – Tillsammans med DSA är vår metod den enda möjligheten att minimera den enorma kostnadsutvecklingen, det är nära nog en dubblering per nod, säger Jonas Sundqvist. Men halvledarindustrin är precis lika försiktig med att införa nya metoder som alla annan processindustri. Ett stopp på grund av att en ny maskin strular kan kosta enorma belopp. Därför är det en stor fördel att företagets metod inte kräver någon ny maskin eller introducerar nya kemikalier. Den kan utföras i befintliga torretsmaskiner från företag som Applied Materials, Lam Research, Tokyo Electron och Hitachi High-Tech. – Vissa av deras processkammarmaskiner kan köra rätt av om man känner till receptet och struktureringen som sker innan. Det är den kunskapen vi säljer och det vi patenterat. Huvudingredienserna är argon och klorgas. Bägge gaserna används i dagens halvledarprocesser. Argon utvinns ur luften tillsammans med syrgas och kvävgas. Halvledarfabrikerna har normalt anläggningar för att göra det lokalt. Klorgas är en standardgas för etsning och det finns alltid utrustning installerad för att hantera den i fabrikerna. I reningsprocessen omvandlas den till saltsyra som också används vid halvledartillverkning så processen skulle kunna vara cirkulär. – Gör man rätt blir det noll utsläpp. |