Både företagen grundades år 2003 och har länge verkat i det tysta. Båda har en ledningsgrupp med veteraner från både FPGA- och EDA-världen. Och både säger sig ha ett recept för hur man kan göra FPGA:er som får in betydligt fler logikblock per ytenhet än vad Xilinx och Altera klarar av.

Men medan Tabula tagit in 107 miljoner dollar från riskkapitalbolagen har Tier Logic klarat sig med 20 miljoner dollar.

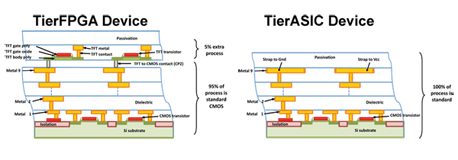

Det eleganta med Tier Logics teknik är att företaget lyfter upp konfigureringen, SRAM-cellerna, i ett separat lager ovanpå logiken (LUT:arna) och arbetsminnet. För att skapa SRAM-cellerna i en FPGA använder Tier Logic tunnfilmstransistorer på amorft kisel i det nionde lagret, en teknik som utvecklats av japanska Toshiba som en gång var Xilinx foundrypartner.

Vill man istället har en asic byter man ut tunnfilmstransistorerna mot ett nionde ledarlager i metall. Det tar visserligen några veckor att göra och kostar en del pengar men eftersom de åtta understa lagren med logik och arbetsminne är orubbade förändras inte uppförandet hos kretsen.

Metoden med att lyfta upp konfigurationen ovanpå logiken leder också till en kompaktare krets. Enligt Tier Logic får man in upp till tre gånger så mycket logik per ytenhet jämfört med konventionella FPGA:er.

Exakt hur många logikblock som kommer att finnas i Tierlogics FPGA-familj vill företaget ännu inte avslöja. Inte heller vilka hårda block, som multiplikatorer eller Serdes, som det kommer att finnas. Eller hur IP-biblioteket ser ut. Företaget säger inte heller något om effektförbrukningen eller vilken klockhastighet som är möjlig att uppnå.

Exakt hur många logikblock som kommer att finnas i Tierlogics FPGA-familj vill företaget ännu inte avslöja. Inte heller vilka hårda block, som multiplikatorer eller Serdes, som det kommer att finnas. Eller hur IP-biblioteket ser ut. Företaget säger inte heller något om effektförbrukningen eller vilken klockhastighet som är möjlig att uppnå.Kretsarna ska dock tillverkas i en mogen 90 nm-process av Toshiba. Det kan jämföras med Xilinx och Altera som kommer med produkter på 28 nm mot slutet av året vilket är ungefär samtidigt som Tierlogics första produkter också når marknaden.

Tier Logic hävdar att tekniken med tunnfilmstransistorer går att skala ner till åtminstone 40 nm.

Den som vill designa med Tier Logics kan använda sina vanliga verktyg som Precision Synthesis från Mentor Graphics. För placering och ledningsdragning, timinganlys och andra hårdvarunära delar av designen får man använda Tier Logics eget verktyg kallat Mobius.