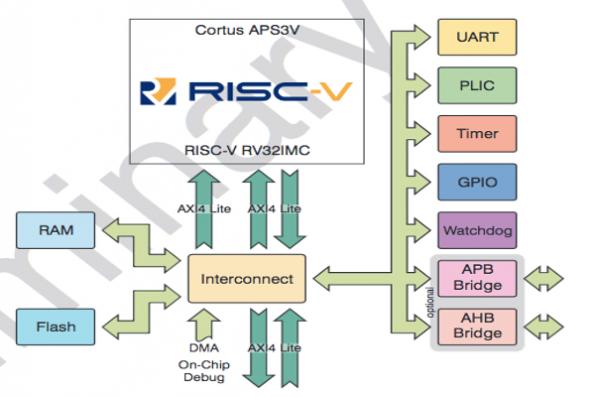

Franska Cortus har skapat sin första RISC-V-cpu genom att helt enkelt skruva lite grand på en existerande egen kärna. Den nya 32-bitars-cpu:n släpps under namnet APS3V.

Franska Cortus har skapat sin första RISC-V-cpu genom att helt enkelt skruva lite grand på en existerande egen kärna. Den nya 32-bitars-cpu:n släpps under namnet APS3V.

Cortus byter ut instruktionsuppsättningen Andestar på sin cpu-kärna APS23 mot RV32IMC, inklusive multiplikation och division. Dessutom ökas antalet register från 16 till 32.

Den nya kärnan kallas APS3V. Produktionsfärdig RTL finns att licensera nu.

Rörledningen ökas från tre till fem eller sju steg vilket är en av orsakerna till att APS3V enligt Cortus ska kunna klockas till 2,2 GHz i 28 nm HKMG – dubbelt så högt som APS23.

I 40 nm UMC ska den kunna klockas i upp till 1,11 GHz, dra 15 µW/MHz och ta upp en yta på 0,028 mm2. Detta ska ge en CoreMark-prestanda på 1,43 Coremarks/MHz.

Cortus är känd för sina kompakta implementationer, och detta ska enligt företaget även gälla APS3V. 8642 grindar plus registerfil ger en summa på cirka 17000 grindar.

Också RISC-V:s kodkomprimering stöds.

Cortex M3 är närmaste värdiga cpu-motståndare i ARM-världen. Men till skillnad från ARM är RISC-V en öppenkodsarkitektur vilket betyder att Cortus inte behövde be någon om lov för att producera APS3V.

RISC-V-cpu:er finns idag också att licensera från Andes och Sifive. Dessutom finns ett antal gratisimplementationer.

Cortus är platinamedlem i RISC-V-stiftelsen och säger sig ha fler RISC-V-kärnor under utveckling.