En cpu optimerad för prestanda och en för strömsnålhet – det är amerikanska veteranen Mips första bidrag till arkitekturen Risc V. Integrera dem till en 512-kärning om du vill.

En cpu optimerad för prestanda och en för strömsnålhet – det är amerikanska veteranen Mips första bidrag till arkitekturen Risc V. Integrera dem till en 512-kärning om du vill.

IP-företaget Mips har bytt risc-arkitektur, om du inte visste det.

Bolaget heter Mips för att det brukade utveckla cpu:er i arkitekturen med samma namn. Men i mars i fjol reste det sig ur askan efter en konkurs och rekonstruerades med ett nytt uppdrag – att designa Risc V-kärnor istället.

Och nu är de första klara för lansering.

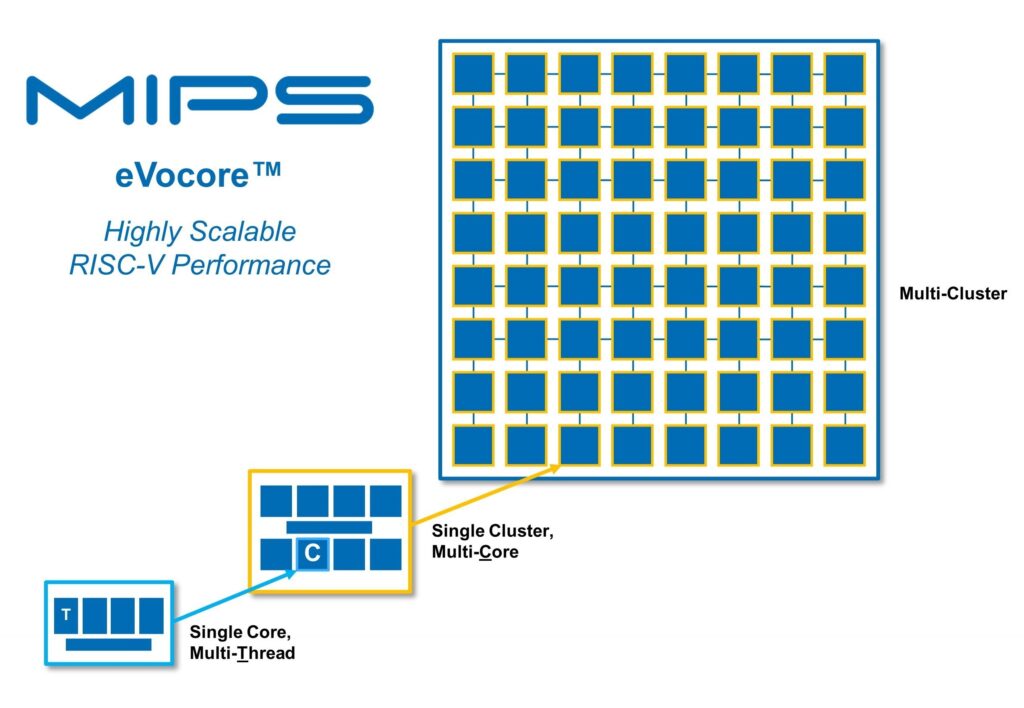

P8700 och I8500 tillhör båda samma produktfamilj, Evocore. De är avsedda för beräkningstunga tillämpningar inom nätverk, datacenter och fordon.

Realtid och hög prestanda är Mips nyckelord för Evocore. Du kan sätta ihop dem till multikärnor med cachekoherens. De stöder virtualisering i hårdvara. Det går att koppla in acceleratorer. Det ska gå att bygga funktionssäkra system av dem och de har hårdvarustöd för debug.

P8700 släpps under fjärde kvartalet år. Den är optimerad för prestanda.

Den säger sig ha den högsta enkeltrådade prestandan bland samtliga Risc V-kärnor. Den släpper instruktioner i oordning om det kan hålla rörledningen bättre fylld och den har parallella spår i samma rörledning.

I8500 är optimerad för strömsnålhet och skulle passa bra i en systemkrets, tycker Mips. I lanseringen står inget datum för när den blir tillgänglig.

Vll du han en parallellprocessor är den skalbar till upp till 64 kluster, 512 kärnor och 1024 trådar. Se bild nedan!

Från första till sista riscMips är en av de klassiska risc-arkitekturerna. Nu lämnas stafettpinnen över till den senaste risc-arkitekturen.

Bolaget Mips har gått igenom många turer. Det brukade konstruera cpu-kärnor i arkitekturen Mips. Affärsmodellen är att andra företag licenserar cpu:erna och integrerar dem i egna chips. I likhet med andra arkitekturer kvävdes Mips i en alltmer dominerande konkurrens från arkitekturen Arm. Idag seglar den fria arkitekturen Risc V upp, till synes ostoppbar på alla fronter. Här finns dock en möjlighet för konkurrenterna att gilla läget genom att helt enkelt börja konstruera egna Risc V-kärnor. Och det var också vad Mips meddelade att det skulle göra när det rekonstruerades i mars 2021. Det finns inga lagliga hinder mot detta och inga avgifter att betala till någon. Det är det som är grejen med öppen källkod. Mips första drag när Risc V dök upp och stal strålkastaljuset var att släppa Mips som öppen källkod. Det var för sent. Mips gick under efter ett antal turer, sist under ägarskap av Mipsprocessortillverkaren Wave, som i slutänden drog med sig Mips i sitt eget fall. Mips är en första generationens risc från 80-talet. Risc V räknar sig som syns på namnet som den femte. MIps är den risc som Risc V mest av allt liknar, enligt Mark Himelstein som är teknikchef på RISC-V International och tidigare jobbat på Mips. Så Mips torde känna sig som hemma i Risc V och designteamet torde ha fått en flygande start med de två första kärnorna. Mips, arkitekturen, är förresten inte död. Du kan fortfarande licensera både arkitektur och äldre cpu-kärnor från Mips, bolaget. |