EMBEDDED WORLD Två prestandaoptimerade Risc-V-kärnor med i det närmaste kompletta uppsättningar av de hittills standardiserade Risc-V-extensionerna – det erbjuds av ryska Cloudbear.

EMBEDDED WORLD Två prestandaoptimerade Risc-V-kärnor med i det närmaste kompletta uppsättningar av de hittills standardiserade Risc-V-extensionerna – det erbjuds av ryska Cloudbear.

I den gemensamma montern för företag i ekosystemet för den öppna processorarkiketuren Risc-V, hittar vi Cloudbear från Sankt Petersburg. Det är ett av de många företag som erbjuder kommersiella Risc-V-kärnor.

Arkitekturen Risc-V är berömd för att den är fri – vem som helst kan bygga en processor som använder Risc-V-instruktionerna gratis och utan att be någon om lov. Trots det – eller tack var det? – finns det ingen annan arkitektur med lika stor bredd i urvalet av kommersiella implementeringar.

Det nya som Cloudbear presenterar på Embedded World i år, är två kärnor i en prestandafamilj kallad BI – en 32-bitare och en 64-bitare. De kan till exempel integreras i systemkretsar för modem, beräkningsacceleratorer, nätverkskort, automation, sd-kortstyrning eller andra tillämpningar som kräver snabba dataflöden eller beräkningar.

Det nya som Cloudbear presenterar på Embedded World i år, är två kärnor i en prestandafamilj kallad BI – en 32-bitare och en 64-bitare. De kan till exempel integreras i systemkretsar för modem, beräkningsacceleratorer, nätverkskort, automation, sd-kortstyrning eller andra tillämpningar som kräver snabba dataflöden eller beräkningar.

Båda är inte bara prestandaoptimerade utan prickar dessutom av nästan alla tillägg till Risc-V som hittills klubbats som standarder. Arkitekturen är närmare bestämt ”RV64-IMCAFDN”- vilket betyder att den stöder i tur och ordning heltalsaritmetik (I) inklusive multiplikation och division (M), komprimerade instruktioner (C), atomära instruktioner (A), flyttal (F) i dubbel precision (D) och sist men inte minst avbrottshantering på user-nivå (N). Alla utom den sistnämnda är frusna standarder.

Det som saknas bland de utökningar som är klubbade är ”Q” – dubbel dubbel precision.

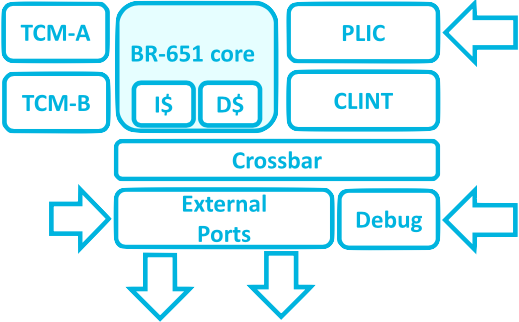

32-bitaren heter BR-351 och 64-bitaren heter BR 651. Deras Dhrystoneprestanda är 2,2 respektive 2,44 poäng per MHz. I TSMC 28HPC+ kan de klockas till 1,2 GHz.

Risc-V:s gruppmonter är uppställd på mässan för tredje året. Risc-V är orsaken till att Cloudbear existerar.

|

| Alexander Kozlov |

–Vi var några stycken som insåg att Risc-V var var en mycket intressant utmanare till Arm, berättar en av företagets grundare, Alexander Kozlov, med en tidigare bakgrund på Samsung.

Cloudbears första Risc-V-implementeringar var kärnor för mikrostyrkretsar (motsvarande ungefär cpu-jätten Arms familj Cortex M) och för app-processorer (motsvarande Cortex A).

Den kärna som Cloudbear licenserat flest av är mikrokärnan BM-310. Den har en trestegspipeline och fysiskt minnesskydd. Den motsvarar ungefär en Cortex M3 ”med lite bättre prestanda”, enligt Cloudbear, och har bland annat fått en design win hos ryska Milandr i en smart elmätare.

BM-310 är kompatibel med debuggingverktyg från IAR, Segger och Lauterbach och kan klockas till 600–700 MHz tillverkad i TSMC 28HPC+.

Risc-V befinner sig under standardisering och Cloudbear är en aktiv medlem i stiftelsen. Där har företaget av naturliga skäl tagit på sig ansvaret att se till att arkitekturen får ett bra stöd för ryska kryptostandarder.

–Och det tror jag att vi kommer att få. Ryska, amerikanska, kinesiska – det ser ut som om alla kommer att få bra stöd, säger Alexander Kozlov.

Stöd för en utökning med vektorinstruktioner (V) i Risc-V ska klubbas i år. Det blir en milstolpe för dem som är intresserade av prestandaberäkningar som grafik, maskininlärning, signalbehandling och simulering.

Vektorinstruktionerna är även viktiga för kryptering, som har en egen arbetsgrupp inom Risc-V-stiftelsen. Alexander Kozlov berättar att vektorgruppen lyssnar noga på krypotogruppens önskemål.