Strax för jul blev det klart att tyska Bosch Sensortec ska använda Xenergics strömsnåla cacheminne i sina mikromekaniska sensormoduler. Uppstartsbolaget överväger nu att ta in mer pengar för att kunna skala upp snabbare.

Strax för jul blev det klart att tyska Bosch Sensortec ska använda Xenergics strömsnåla cacheminne i sina mikromekaniska sensormoduler. Uppstartsbolaget överväger nu att ta in mer pengar för att kunna skala upp snabbare.

– Bosch är den första kunden vi kunnat gå ut och berätta om, säger Anders Berglund som är styrelseordförande i Xenergic.

Företaget grundades så sent som i augusti 2017 av Babak Mohammadi tillsammans kollegan Joachim Rodrigues, entreprenören Anders Berglund och Lunds universitets holdingbolag.

– Vi satt och gjorde en skattning av vad de kunder vi har i pipeline skulle kunna generera. Då räknade vi till över en halv miljard.

Siffran som Anders Berglund nämner förutsätter att alla förfrågningar omvandlas till beställningar.

I uppskattningen ingår startkostnad och royalty under tre till fem år efter det att en krets börjat tillverkas. Affärsmodellen är den gängse i IP-världen och innebär att det redan börjat ticka in pengar för bolaget.

I uppskattningen ingår startkostnad och royalty under tre till fem år efter det att en krets börjat tillverkas. Affärsmodellen är den gängse i IP-världen och innebär att det redan börjat ticka in pengar för bolaget.

Hittills är minnet kvalificerat hos fem halvledartillverkare. Det handlar om 15 processnoder från 152 nm ner till 16 nm FinFET där Xenergic fått tillgång till transistormodeller och designregler för att kunna verifiera sitt IP-block.

– Det går väldigt fort och går åt väldigt lite resurser för att anpassa till en ny process. Vi gör det på under två månader, säger Anders Berglund.

Normalt i branschen är att den här typen av arbete tar ett år eller mer.

Arbetsminnen kommer vanligen med en minneskompilator men går trots det inte att modifiera för att passa en specifik tillämpning, de kan i princip betraktas som standardprodukter.

Xenergic har utvecklat en egen minneskompilator kallad MemoryTailor som automatiserat levererar skräddarsydda minnen. Konstruktören matar in olika parametrar och kompilatorn designar sedan det mest optimala minnet utgående från dessa förutsättningar.

Artikeln är tidigare publicerad i magasinet Elektroniktidningen. Artikeln är tidigare publicerad i magasinet Elektroniktidningen.Prenumerera kostnadsfritt! |

Resultatet blir modeller som beskriver funktionen hos minnet plus en layoutfil för den aktuella processen. Kunden använder resultaten i sitt layoutverktyg där systemkretsen designas.

Idag arbetar ungefär 20 personer för Xenergic som tagit in runt 15 miljoner från bland annat Almi Invest och LU Holding på Lunds universitet.

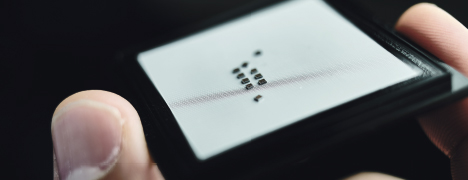

Så fungerar detI en systemkrets kan cacheminnet utgöra 70 procent av ytan och stå för mer än halva energiförbrukningen.

– Med vår lösning kan vi sänka energiförbrukningen i hela kretsen med mellan 70 och 90 procent, beroende på vilka krav som ställs på slutprodukten, säger Babak Mohammadi. Tekniken bygger på forskning kring strömsnåla minnen som han bedrivit under tio års tid på institutionen för Elektro- och informationsteknik vid Lunds tekniska högskola. Lösningen sänker både den statiska och den dynamiska effektförbrukningen så exakt hur stor besparingen blir beror på hur minnet används. Störst besparingspotential finns i det statiska läget, när minnet inte används. Men även den dynamiska strömförbrukningen vid läs- och skrivoperationer blir avsevärt mindre. Normalt brukar man sänka matningsspänningen för att få ned strömförbrukningen i en halvledarkrets. Tekniken har länge använts för processorkärnor trots att en lägre matningsspänning samtidigt leder till att den användbara klockfrekvensen sjunker. På arbetsminnen har det inte fungerat eftersom den användbara klockfrekvensen sjunker mycket snabbare för ett SRAM än för processorkärnan. I ett designexempel som presenterades på Cadence Live i oktober förra året låg arbetsspänningen på 0,6 V med en klockfrekvens mellan 200 och 500 MHz i en 28 nm-process. – Det är något som de andra inte kan komma nära. Normalt behöver man mellan 0,8 V och 0,9 V för 200 till 500 MHz. – Hela systemet blir mycket enklare. – Att bara sänka spänningen, det kan många. Vi kan sänka den och behålla frekvensen, då får man prestanda som är intressant, säger Babak Mohammadi och fortsätter: – Folk brukar vara glada om det minskar med en eller två procent, vi gör det med 70 till 90 procent. |