Intels första teraflopsprocessor ska använda x86:or och acceleratorkärnor ihopkopplade i ett nätverk. Terascale Computing Group är Intels största forskningsgrupp med 225 forskare. Om 5–10 år ska deras resultat finnas i processorer för pc och server.

Intels första teraflopsprocessor ska använda x86:or och acceleratorkärnor ihopkopplade i ett nätverk. Terascale Computing Group är Intels största forskningsgrupp med 225 forskare. Om 5–10 år ska deras resultat finnas i processorer för pc och server.Intel talar om forskningsområdet som "Terascale Computing" eftersom både prestanda i operationer per sekund och genomströmning i byte per sekund ska ligga i storleksordingen en biljon.

I dagens multikärnor från Intel sitter bara x86-kärnor. Men det är inte det effektivaste sättet att använda transistorer i en processor som ska leverera biljoner operationer per sekund. Så i Intels NoC kommer kärnorna kommer att vara av blandat slag. TCP-IP-processorer, flyttalsmaskiner och rekonfigurerbara viterbialgoritmer är några typer av acceleratorer som Intel nämner som exempel.

Dessutom kan trådhantering komma att få hårdvarustöd, främst för att man ska kunna arbeta med små trådar för finkornigare parallellism.

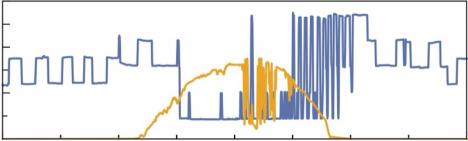

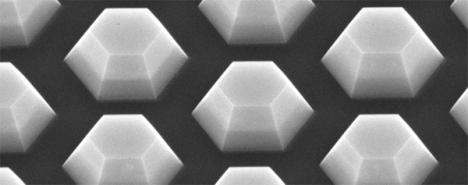

80 kärnor i testchip Första delmålet är nått, att implementera ett chip som klarar en biljon flyttalsoperationer per sekund på en effektbudget som ligger i nivå med dagens skrivbordsdatorer. Första delmålet är nått, att implementera ett chip som klarar en biljon flyttalsoperationer per sekund på en effektbudget som ligger i nivå med dagens skrivbordsdatorer.Experimentprocessorn Polaris levererar en teraflops i 3,16 Ghz när den drar 62 watt. Klockan kan skruvas ända upp till 5,7 Ghz och 265 watt, men mest effektiv är konstruktionen i 400 MHz där den levererar 394 gigaflops på 20 watt. Processtorleken är 65 nm och den har åtta kopparlager. Hela chipet mäter 275 mm2. Den är inte mycket till skrivbordsdator. Den klarar bara vissa välavgränsade beräkningsuppgifter. Och programvaran med teraflopsprestanda är handkodad. Intel har klipp-och-klistrat 80 identiska byggblock i ett rutnät. Varje block har 1,2 miljoner transistorer och innehåller en router, två flyttalsenheter som summerar produkter, 3 kbyte programminne och 2 kbyte dataminne. Routern är kopplad i de fyra väderstrecken, till angränsande block, och till det egna blocket. Och uppåt i totalt 8490 genomgående vior som i framtiden ska kopplas till ett stackat minneschips. Närheten ska ge korta fördröjningar och mångfalden av vior ska ge hög genomströmning, i storleksordningen terabyte/s hoppas Intel. Här finns ingen global klockpuls. Kärnorna arbetar "mesokront", vilket betyder att de går på samma frekvens oberoende av varandra. I kommunikationen klarar de att hantera situationen att de befinner sig ur fas med varandra. |

Effekthanteringen - energy management - är ett delmål som klistrats upp på pannan på alla delgrupper. Knepen för att spara energi är många.

Kärnorna ska ha individuell spänning och frekvens, och ska kunna sövas ner i två nivåer – med och utan minnesbevarande. Intel gör egen forskning på spänningsregulatorer för att nå målet. Regleringen ska ske minst tio gånger snabbare än idag, vilket skär bort strömmen som förbrukas i ramperna mellan två nivåer i en tillståndsväxling.

Om programmeraren inte lyckats aktivera samtliga kärnor på processorn, till sin algoritm, kommer kärnorna att kasta algoritmen runt mellan sig, för att sprida ut värmen på chipsytan och därmed tillåta högre frekvenser. Tekniken kallas "core hopping".

Idealt ska distributionen av beräkningstrådar på chipets kärnor vara helt dynamisk. En beräkningsintensiv tråd går till en sval kärna medan en mindre kritisk beräkning kan få kyla ner en het kärna.

Kärnorna på chipet ska kunna indelas i separata regioner som hanterar varsitt program. Nätverkstrafiken ska inte korsa gränserna mellan regionerna. Dels för att programmen inte ska störa varandras prestanda och dels som ett sätt att implementera säkerhetspolicies, för att programmen inte ska kunna tjuvkika på varandras information.

Om en kärna plötsligt slutar fungera ska regionerna kunna ritas om. Och reservkärnor ska kunna kallas in.

En stor del av forskningsprojekten i Intel Terascale Computing handlar om mjukvaran. Intel har bland annat tagit fram ett nytt programspråk kallat Ct (C terascale). Distributionen av ett program på multikärnan ska skötas automatiskt. Målet är att programmeraren ska kunna fortsätta tänka seriellt.

Processorn kommer att ha nya instruktioner, exempelvis för att söva och väcka andra kärnor.

Mycket av Intels terascaleforskning publiceras i Intel Technology Journal (länk )