De två japanska elektronikjättarna Panasonic och Renesas har tillsammans tagit fram process- och kretsteknik för halvledare med geometrier på 32 nm. Massproduktion står för dörren.

Nya material och ny teknik krävs när halvledarvärlden går från 40 till 32 nm geometrier i produktionen. Något som är tekniskt svårt och därtill dyrt, vilket förmår halvledarvärlden till ökat samarbete. Senaste budet i raden är japanska Panasonic och Renesas, som förlängt sitt redan tioåriga samarbete till ytterligare en processgeneration.

Samarbetet har löpt på så bra att de båda väntar sig massproduktion på 32 nm "inom kort". Lite beroende på vad det uttrycket innebär kan de båda bli först i världen med massproduktion av kommersiella kretsar vid 32 nm.

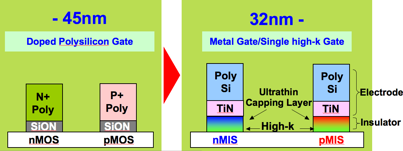

Processen som de båda utvecklat bygger på transistorer med stackade metallgrindar med högt k-värde, och kontakter mellan transistorerna med ett ultralågt k-värde. Transistortypen kallas CMIS3, en variant av CMOS där ett ytterst tunt isolerande täckskikt (cap layer) - några få atomlager oxiderat kisel - läggs på grindstrukturen för att justera transistorns tröskelvärde. Täckskiktet har enligt bolagen visat sig förbättra tillförlitligheten och minska transistorernas inbördes påverkan av varandra.

Tekniken ska användas för system på kisel till mobila tillämpningar och för digital konsumentelektronik.

Bland de två parternas tidigare framsteg märks den första 130 nm DRAM-kretsen 2001, en 90 nm system på kisel-process 2004, samt motsvarande för 65 och 49 nm, 2005 respektive 2007.