Den fabrikslösa halvledartillverkaren Sifive har provexemplar av ett chip med fyra stycken U54-kärnor i cpu-arkitekturen RV64GC. Sifive jämför U54 med Cortex A35, ARM:s lättviktigaste 64-bitare.

Den fabrikslösa halvledartillverkaren Sifive har provexemplar av ett chip med fyra stycken U54-kärnor i cpu-arkitekturen RV64GC. Sifive jämför U54 med Cortex A35, ARM:s lättviktigaste 64-bitare.

Den första öppna arkitektur som på allvar tros kunna utmana ARM finns nu i en 64-bitars fyrkärna som kan köra Linux. Därmed tar RISC-V ett steg upp mot tillämpningar som kräver mer beräkningskraft.

RISC-V-arkitekturen i sig är licensfri och gratis, till skillnad från ARM-kärnorna från konkurrenten med samma namn.

SKAPA CPU UTAN ATT BLI STÄMD |

|

Sifive kommer att släppa fler syskon till U54 i en familj kallad ”Freedom Unleashed”. Vilken frihet är det som släpps loss? Jo, friheten att konstruera en processor som använder en standardarkitektur utan att be någon om lov. Den som försöker sälja en cpu som använder någon av de stora instruktionsuppsättningarna – som ARM, MIPS eller x86 – blir stämd. Denna frihet är historiskt ny. Den har funnits i princip i arkitekturer som Openrisc. Men inte i praktiken eftersom ingen tidigare lyckats komma upp i den kritiska massa av intressenter som krävts för att nå en konkurrenskraftig nivå. RISC-V skapades av nestorer inom processorarkitektur – några av dem finns i Sifive – och fick omedelbart ett brett stöd både inom öppen hårdvara och i halvledarbranschen. |

Cpu-kärnan U54 är inte gratis. Den är en av Sifives implementationer av RISC-V, närmare bestämt av 64-bitarsarkitekturen RV64GC.

Det som Sifive låtit tillverka är ett U54-chip som du kan utvärdera för att kunna bestämma om du vill licensiera U54 till ditt eget chip.

Sifives chip heter U54-MC Coreplex och är klockat till 1,5 GHz. Sifive anger prestanda till 2,75 Coremark/MHz.

Chipet tillverkas i TSMC:s 28 nm HPC. Varje U54-kärna använder 0,234 kvadratmillimeter, eller 0,538 om man inkluderar cache, debug och interrupt.

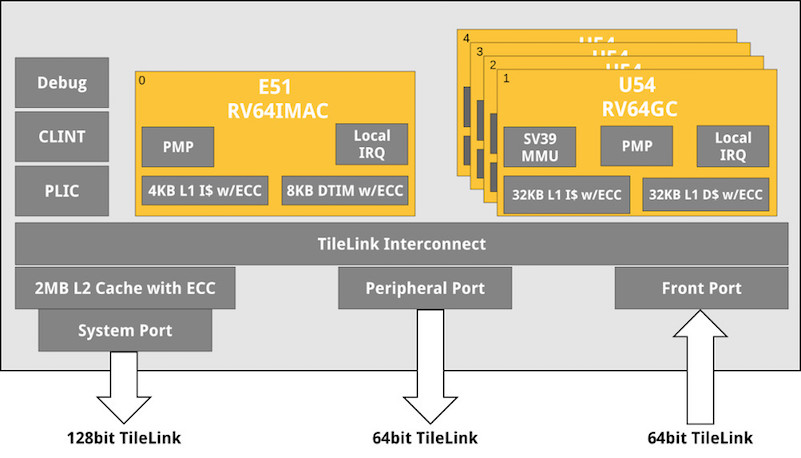

På chipet finns förutom den cachekoherenta fyrkärnan en mindre E51-kärna med arbetsledarfunktion, som exempelvis kan låta U54:orna sova när deras insatser inte behövs.

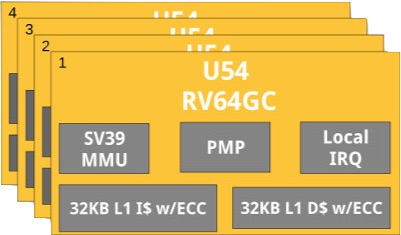

U54 har en pipeline på fem steg och 32+32 kbyte L1-cache. Fyrkärnan delar på 2 Mbyte L2-cache.

U54 kan realtidskonfigureras vilket innebär att man byter hatt på det indeterministiska cacheminnet och låter det fungera som ett snabbt lokalt SRAM istället.

|

| Utvecklingskort med 64-bitaren släpps under första kvartalet 2018. |

Bussgränssnittet heter Tilelink. Det finns adaptrar för AXI4, AHB-Lite och APB om du har några gamla sådana kärnor som du vill haka på.

Sifive jämför U54 med ARM Cortex A35. Jämförelserna handlar – förstås – om U54:as styrkor. Båda är 64-bitare men U54 kan spara bandbredd genom att köra 16-bitarsinstruktioner där A35 stannar vid 32 bitar.

Monitorkärna och interruptstyrenhet ingår, medan det är ett tillval i A35, som heller inte har någon motsvarighet till U54:s realtidskonfigurering.

Båda har MMU (en minneshanteringsenhet som bland annat hindrar program från att använda varandras minne), men A35 har dessutom PMP (Physical Memory Protection), som innebär att regioner av RAM-minnet helt kan spärras för läsning, skrivning eller exekvering. PMP stöter bort buggar och är en försvarsmur mot cyberrattacker.

Enligt tidningen EE Times har flera företag redan licensierat U54, inklusive militära kunder och stora halvledarbolag, för tillämpningar som teveboxar och acceleratorer i datacenter.