ORConf 2024 RISC-V var naturligtvis representerat på olika sätt med en bredd från stora beräkningsenheter ner till små inbyggda processorer.

ORConf 2024 RISC-V var naturligtvis representerat på olika sätt med en bredd från stora beräkningsenheter ner till små inbyggda processorer.

Denna rapport Denna rapportfrån ORConf 2024 är tidigare publicerad i magasinet Elektroniktidningen. Prenumerera kostnadsfritt! |

Vi erbjöds en titt på en sprillans ny RISC-V-kompatibel vektorenhet vid namn Saturn från Berkeley. Av alla instruktionstillägg för RISC-V är just vektorinstruktionerna det som har fått mest uppmärksamhet eftersom det antas kunna ge en rejäl prestandaförbättring för maskininlärning och det är mycket aktivitet kring detta både på hårdvaru- och mjukvarusidan.

Det fanns också RISC-V-veteraner representerade i form av VexIIRiscv, uppföljaren till VexRiscv som är en av de absolut mest populära RISC-V-implementationerna i mellanklassen.

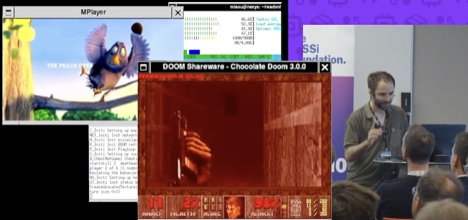

Precis som föregångaren finns VexIIRiscv tillgänglig som Linuxkompatibel multikärna men är numera också 64 bitar. Detta var antagligen den modigaste presentationen på hela konferensen då presentatören valde att köra hela sin presentation samt att köra DooM, Quake och visa film direkt från ett FPGA-kort som implementerade ett VexIIRiscv-baserat system.

Hela uppvisningen gick dessutom problemfritt. Från RISC-V-lägret fanns också en ny processor vid namn FazyRV som har som uttalad ambition att täcka upp storleks- och prestandagapet som finns mellan SERV, världens minsta RISC-V-processor och klassiska lättviktsriscfemmor som Picorv32.

Precis som SERV är FazyRV bitseriell, men kan även konfigureras till att jobba med 2, 4 eller 8 bitar i taget.