Superdatorer och datacenter visar intresse för att använda RISC-V. Det är möjligheten att skräddarsy hårdvaran som lockar.

Superdatorer och datacenter visar intresse för att använda RISC-V. Det är möjligheten att skräddarsy hårdvaran som lockar.

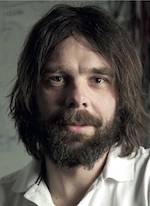

Olof Kindgren är aktiv inom öppen hårdvara som utvecklare, som styrelsemedlem i FOSSi Foundation och som ambassadör för RISC-V International, med mera. Han jobbar på svenska utvecklingsbolaget Qamcom. Olof Kindgren är aktiv inom öppen hårdvara som utvecklare, som styrelsemedlem i FOSSi Foundation och som ambassadör för RISC-V International, med mera. Han jobbar på svenska utvecklingsbolaget Qamcom.Texten är tidigare publicerad i Elektroniktidningen. |

Den gängse teorin om RISC-V:s framtid har varit att den kommer att smygas in som icke-kritiska hjälpprocessor på djupt inbyggda system, för att först därefter börja arbeta sig uppåt i näringskedjan.

Men det verkar snarare bli en attack på flera fronter.

En stor del av RISC-V-veckan i Paris ägnades åt de senaste framstegen inom HPC (High Performance Computing) där RISC-V verkar ha hittat många vänner.

Det som nämns som den stora fördelen hos RISC-V är möjligheten att i högre utsträckning skräddarsy instruktionsuppsättning och hårdvara för att passa specifika tillämpningar.

Det som nämns som den stora fördelen hos RISC-V är möjligheten att i högre utsträckning skräddarsy instruktionsuppsättning och hårdvara för att passa specifika tillämpningar.

För många HPC-applikationer är prestandan för vektorberäkningar central och flera presentationer berörde forskning och nya implementationer av vektoracceleratorer för RISC-V.

Mycket av arbetet utförs av BSC (Barcelona Supercomputing Center) inom EPI-projektet (European Processor Initiative). Även ETH Zürich och kommersiella aktörer som Semidynamics presenterade processorer, acceleratorer och forskning med sikte på HPC.

En intressant aspekt värd att notera är att ARM:s snabba intåg i HPC-världen har öppnat dörrar för RISC-V genom att visa att alternativa instruktionsuppsättningar och RISC-arkitekturer fungerar alldeles utmärkt även för högprestandatillämpningar.