Det går alldeles utmärkt att använda öppna och därmed kostnadsfria EDA-verktyg för att lära studenterna att designa analoga kretsar. En grupp doktorander på Uppsala universitet bevisade det i våras och förhoppningen är att införa kursen även för ingenjörsstudenterna på E och F-programmen.

Det går alldeles utmärkt att använda öppna och därmed kostnadsfria EDA-verktyg för att lära studenterna att designa analoga kretsar. En grupp doktorander på Uppsala universitet bevisade det i våras och förhoppningen är att införa kursen även för ingenjörsstudenterna på E och F-programmen.

Ted Johansson

|

Mikroelektronik ingår numera i nästa alla produkter och det finns därför ett stort behov av utbildade ingenjörer och forskare som förstår halvledare, kretselektronik och allt däremellan upp till komplexa system.

Det behövs också vidareutbildning för redan yrkesverksamma ingenjörer. Kurser inom elektronik, halvledare, krets- och chipkonstruktion samt tillverkningsteknik behöver skapas eller förnyas på olika nivåer, från vidareutbildning av yrkesverksamma, ingenjörsutbildningsprogrammen till forskarutbildning.

När man vill utbilda ingenjörsstudenter och forskarstuderande i chipkonstruktion är det viktigt att skilja på yrkesutbildning, där studenterna avser att arbeta med chipkonstruktion på olika företag och det därför är viktigt att utbilda så mycket som möjligt med de verktyg som används i industrin, och vad jag skulle kalla orienterande utbildning där principerna för konstruktionsflöden och verktyg är det viktiga men man inte nödvändigtvis behöver använda de kommersiella verktygen om det finns alternativ.

Kommersiell chipkonstruktion görs i ett konstruktionsflöde med verktyg från ett begränsat antal aktörer, i huvudsak Cadence, Synopsys och Mentor (Siemens). Beroende på om det är analoga/RF-kretsar eller digitala kretsar, ser flödena och verktygen helt olika ut. I denna artikel behandlas analoga kretsar, flöde och verktyg. Analoga konstruktionsflöden är mindre komplexa än de digitala, så även själva kretsarna. Däremot behövs mycket simuleringar för att hitta bra och robusta kretslösningar.

Tillgång till de kommersiella verktygen medför ofta stora initiala kostnader, även med starkt reducerade licenskostnader för universiteten, vilket gör det intressant att undersöka om flöden och verktyg baserade på öppen programvara skulle kunna används för orienterande utbildning. Vi har därför satt upp en doktorandkurs i analog chipkonstruktion på Uppsala universitet, enbart baserat på öppna verktyg och processinformation, och gett den under våren 2024.

Öppen programvara för elektronikkonstruktion har gamla anor. Spice till exempel, som utvecklades på Berkeley – första versionen kom 1973 – hade fokus på analog IC-konstruktion och källkoden släpptes i ”public domain” redan från början. De flesta av dagens simulatorer för konstruktion av analog IC (och med kommersiella diskreta komponenter för PCB-baserad elektronik) är baserade på Spice.

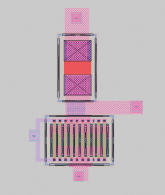

För ett analogt IC-konstruktionsflöde behövs verktyg för schemaritning, kretssimulering, layout, verifieringar, generering och inspektion av maskdata. För schemaritning finns verktyget xschem, för kretssimulering ngspice, för layout magic (även layoutverifiering, DRC) och KLayout, för schema-layoutverifiering (LVS) netgen. magic går även att använda för parasitextraktion (PEX). Generering av maskdata görs med magic och återläsning för verifiering och inspektion kan med fördel göras med KLayout.

För ett analogt IC-konstruktionsflöde behövs verktyg för schemaritning, kretssimulering, layout, verifieringar, generering och inspektion av maskdata. För schemaritning finns verktyget xschem, för kretssimulering ngspice, för layout magic (även layoutverifiering, DRC) och KLayout, för schema-layoutverifiering (LVS) netgen. magic går även att använda för parasitextraktion (PEX). Generering av maskdata görs med magic och återläsning för verifiering och inspektion kan med fördel göras med KLayout.

Alla programmen är öppna och underhålls aktivt. Support ges för ett par av programvarorna i samarbetsplattformen Slack, både av communityn men även direkt av programansvariga.

Installation av programmen var inte trivial; ofta behövdes källkoden lyftas ned från github och kompileras. Verktygen och flödet i vår kurs utgår från en liknande kurs från KCAST (King Abdulaziz City for Science and Technology, Saudiarabien) som hade bra material för hur de olika verktygen skulle sättas upp med Linux Ubuntu. Även om vissa av verktygen finns för både Windows, Linux (och även Mac i några fall), underlättar det för hela flödet om Linux används. Vi hade både en central Linux-server (Centos7 med ThinLinc) men också virtuella maskiner (VirtualBox med Ubuntu och AlmaLinux) som studenterna kunde ladda ned till sina egna datorer och köra lokalt. Eftersom all programvara är öppen är det inga problem med att göra kopior, licenser, etc.

Den kritiska informationen för att verkligen kunna konstruera chip (och även få dem tillverkade) är tillgång till en PDK (process design kit) för en IC-process som också har utförlig dokumentation. Detta är information som foundries (kiselsmedjor) har hållit mycket hårt i, med komplicerade NDA:er och restriktioner för tillgång till manualer, etc. Google har genom Open PDK Initiative lyckats övertyga ett par foundries att göra denna information öppen och skapa nedladdningsbara PDK:er för konstruktion, layout och verifiering samt sponsra ett antal fria MPW (multiproject wafer)-körningar. SkyWater Technologies 130 nm och 90 nm CMOS, GlobalFoundries 180 nm CMOS och nu senast IHP 130 nm BiCMOS är de processer som finns tillgängliga på detta sätt och fler verkar vara på gång.

Vi valde SkyWater 130 nm CMOS, som var den första PDK:n att göras öppet tillgänglig och därför kanske den mest beprövade. Det är en ganska typisk IC-process för inte alltför krävande konstruktioner men med många utökningar för den som önskar exempelvis minnen, specialkretsar eller högspända komponenter. Installationen av PDK:n var ganska tidskrävande med långa kompileringar och stort behov av minne, men gick utan problem. Det går att installera en delmängd av PDK:n om man bara behöver den analoga delen, men eftersom dagens analoga kretsar ofta har digitala delar som en del av en större IC-konstruktion (mixed-signal), installerades allt.

Fokus för kursen är konstruktionsflöden, verktyg och mycket annat som är bra att veta när man ska konstruera chip och få prototyper tillverkade, mestadels små kretsar för forskning eller liknade. Däremot är inte fokus på själva elektronikkonstruktionen; det förutsätts att kursdeltagarna har grundläggande kunskaper i elektronik, kretsanalys och komponenter. Känner de till något om tillverkningsteknik, CMOS-processer, kan förstå ett tvärsnitt av en komponent och varför man har olika masklager är det bra men inte nödvändigt. En mycket enkel analog krets, en common-source-förstärkare (en transistor och en resistor), användes som exempelkonstruktion. Som examination valde vi att låta studenterna konstruera en egen krets, vald från en lång lista med små analoga kretsar med bara två transistorer (Pretl & Eberlein, IEEE Solid-State Circuits Magazine, 2-2021). En rapport med schema, simuleringar, layout, godkända verifieringar och slutligen en gds-fil (det som skickas till ett foundry för tillverkning) utgjorde underlaget för examinationen.

Författaren har erfarenhet av konstruktion i CMOS av analoga- och RF-kretsar från industri och akademi i noder från 350 nm ned till 28 nm. Det dominerande kommersiella verktyget är Cadence Virtuoso för schema, layout, maskgenerering och inspektion samt verktyg från Cadence eller Mentor för verifiering.

Intrycket av de öppna verktygen i jämförelse med de kommersiella är gott i de flesta fallen. Flödet ser i många delar ut på samma sätt och de flesta öppna verktygen fungerar bra för syftet. Det är dock mindre integration av schema/simulering/hantering av designceller än i Cadence, utan får ske direkt i Linux med hjälp av mappar.

En svag punkt är layoutprogrammet magic som inte är modernt eller enkelt att använda, speciellt när kretsar börjar bli lite mer komplexa och layouten ska göras kompakt och snygg. Den interaktiva layoutkontrollen (DRC) är dock trevlig och lätt att använda.

Jämförelsen av krets/layout med/utan parasiter kräver manuell editering av nätlistor, något som Cadence verktyg klarar utan problem.

Slutligen, PDK:n från SkyWater är väl integrerat i schema- och layoutprogram. Däremot fanns det problem med bland annat resistormodeller som genererade olika resultat i schema och layout, vilket krävde handpåläggning för att få LVS godkänd (känt problem). Dokumentationen är inte heller i klass med motsvarande information från stora foundries som IBM eller TSMC, men tillräcklig bra för vårt syfte. Med supporten via diskussioner i Slack kunde vi lösa de frågor som uppkom och även rapportera en bugg i magic! En stark och engagerad community, direkt kontakt med ansvarig för programmen och snabba buggfixar är ofta fördelar med öppen programvara och så även här.

Det finns möjlighet att få sina chip tillverkade genom företaget Efabless i form av Multi-Project Wafers (MPW) eller via projektet Tiny Tapout, speciellt inriktat för universitet och utbildning, där en större mängd mycket små konstruktioner (huvudsakligen digitala) samsas på en mycket liten yta med standardiserat gränssnitt för signaler. Med en startkostnad på 500 dollar för upp till fem små projekt som levereras monterade på ett kretskort, är detta en mycket låg kostnad för en första chipkonstruktion ”på riktigt”!

Intrycket av de öppna verktygen i jämförelse med de kommersiella är gott i de flesta fall, även om vissa verktyg inte håller samma klass som de kommersiella. Dokumentationen av process- och konstruktionsregler är också lite mager men fungerar för ändamålet.

För en orienterande kurs i analog IC-konstruktion och hur man får prototyper tillverkade vid ett foundry fungerar konstruktionsflödet, de öppna verktygen och processinformationen utan större problem. Min egen erfarenhet av de kommersiella programvarorna är att de inte heller är helt perfekta och ibland inte uppdaterade på länge för denna typ av IC-konstruktion.

Våra doktorander hade inga större problem att följa kursen och konstruera egna små kretsar, verifierade och godkända för tillverkning. Över lag var de nöjda med kursen och vad de lärde sig. Vi hade inte heller några större problem med flöden, verktyg, installationer och dokumentation, även om det var många olika programvaror som skulle samverka.

Artikeln är tidigare publicerad i magasinet Elektroniktidningen. Artikeln är tidigare publicerad i magasinet Elektroniktidningen.Prenumerera kostnadsfritt! |

En student i denna första kurs planerar att få AD- och DA-block tillverkade under hösten. Det tar runt fem månader att få tillbaka chip för utvärdering, vilket är jämförbart med prototypchip från rent kommersiella aktörer, exempelvis via organisationen Europractice som universitet i hög grad annars använder sig av.

Vår förhoppning är att även ge kursen för ingenjörsstudenter för E och F-programmen på avancerad nivå (år 4/5) inom en snar framtid.

är docent och universitets- lektor i fasta tillståndets elektronik vid Uppsala universitet. Han har 40 års erfarenhet av R&D och utbildning om halvledarkomponenter och analog/RF-kretskonstruktion från forskningsinstitut, industri och universitet.

är docent och universitets- lektor i fasta tillståndets elektronik vid Uppsala universitet. Han har 40 års erfarenhet av R&D och utbildning om halvledarkomponenter och analog/RF-kretskonstruktion från forskningsinstitut, industri och universitet.