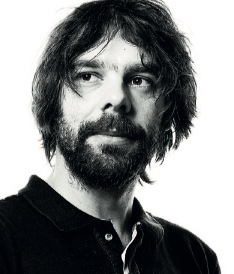

Hans senaste projekt inom öppen hårdvara blev hux flux grunden för en universitetskurs i datorarkitektur. Elektroniktidningen har pratat med Olof Kindgren, veteran inom öppen hårdvara.

Hans senaste projekt inom öppen hårdvara blev hux flux grunden för en universitetskurs i datorarkitektur. Elektroniktidningen har pratat med Olof Kindgren, veteran inom öppen hårdvara.

När IP-leverantören Imagination skulle ta fram en universitetskurs i datorarkitektur valdes en FPGA-version av Swerv (SweRV) som grunden. Det är en Risc V-processor från amerikanska hårddisktillverkaren Western Digital (WD).

Referensplattformen som används i kursen utvecklades i fjol för WD:s räkning under ledning av Olof Kindgren på konsultbolaget Qamcom. Han är veteran inom öppen hårdvara.

– Jag tycker självklart att detta är superkul! Det har visserligen funnits universitetskurser som har använt öppna processorer länge – Linköpings universitet hade till exempel kurser baserade på OpenSPARC och OpenRISC för snart 20 år sedan – men det har inte funnits några satsningar av den här storleken förut, säger han.

Kursen som använder Olofs plattformImaginations kurs heter ”RVfpga: Understanding Computer Architecture” och beskrivs som en komplett kurs i Risc V, inklusive lektioner och labbövningar. Kursen blir ett av momenten i Imaginations utbildningsprogram IUP (Imagination University Program). Den kommer att finnas på engelska i november, och senare på kinesiska, japanska och spanska. |

ARKITEKTUREN RISC V har sedan några år tagit huvudrollen inom öppen hårdvara – den har blivit dess ”Linux”. Den skapades för undervisning men används allt oftare kommersiellt och utmanar idag kommersiella IP-kärnor.

SWERVOLF (SweRVolf) heter Olof Kindgrens referensplattform, som under kursen körs på en FPGA. Swerv och Swervolf är liksom Risc V öppen källkod. Det är därför det är möjligt att skapa en kurs som samtidigt adresserar både SoC-utveckling och cpu-konstruktion. En övning på kursen kan typiskt bestå i att göra en modifiering av Swervolf.

– Den togs fram för att det skulle vara lättare att komma igång med designer som använder Swerv, oavsett om man är mjukvaruutvecklare och bara behöver ett färdigt system, eller om man är hårdvaruutvecklare och behöver en plattform att bygga vidare på.

Swervolf använder Swervversionen EH1. Varianter med Swerv EL2 och EH2 är under utveckling. Första versionen av Swervolf släpptes för ett år sedan med stöd för Digilents Nexys A7-kort.

– I framtiden räknar jag med att man ska kunna köra Swervolf på kort från de flesta FPGAleverantörer.

Swerv EH1 är en öppen kärna under Apachelicens skriven i System Verilog. Den har uppbackning från Chips Alliance – en organisation för öppen hårdvara – där både Western Digital och Qamcom är medlemmar.

– Just kombinationen av en öppen kärna skriven i ett traditionellt HDL med uppbackning av ett stort konsortium verkar väcka stort intresse, säger Olof Kindgren.

Filerna kan tankas hem från Chips Alliance, en organisation för öppen hårdvara. Tjeckiska Codasip erbjuder kommersiell support runt Swerv och Swervolf.

Swervolf skapades på pakethanteraren FuseSoC – ett äldre projekt med Olof Kindgren som skapare.

BIDRAGEN KOMMER i övrigt från massor av håll. AXI-infrastrukturen kommer från ETH Zürichs PULP-projekt. UART och SPI-controller utvecklades ursprungligen för OpenRISC för snart 20 år sedan. DDR2-interface kommer från Enjoy Digital.

– Som grädde på moset sitter världens minsta Risc V-processor – den prisbelönta Serv – som hjälpprocessor i DDR2-controllern, berättar Olof Kindgren.

Serv (SERV) är ytterligare en av hans egna skapelser. På Twitter har det gått att följa hans rapporter om hur han i ett lekfullt experiment kämpat med att trycka in fler och fler Serv i en och samma FPGA. Skapelsen heter Plenticore och han kallar den skämtsamt för en plattform för ”ultraineffektiva flyttalsberäkningar”. Just nu ligger han på 5 857 stycken Serv-cpu:er på ett chip.