Nästa Arm är två:

Nästa Arm är två:

en snabb, en snål

En strömsnål cpu och en snabb cpu på samma chip – så blir nästa generations Armprocessorer både snabbare och strömsnålare än dagens. Arms standardlösning heter Big Little.Det här är ett växande problem för dem som konstruerar processorer för smarttelefoner och pekplattor.

Deras processorer blir allt kraftfullare och slösar därmed alltmer på batterierna när de går enklare ärenden. De är dimensionerade för häftiga spel och augmented reality men ägnar det mesta av sin tid åt simpel telefonering, surfning och e-post.

Stora processorer kan i viss utsträckning spara energi genom att dra ner spänning och klockfrekvens. Men en dragster blir inte en ekobil hur mycket du än sänker varvtalet. Dessutom sjunker skillnaden mellan min- och maxspänning för varje processgeneration, så utrymmet för reglering den vägen sjunker.

Lösning från UCSD

År 2003 presenterades lösningen på problemet av ett forskarlag på UCSD-universitetet. Alla slog sig för pannan. För lösningen var med facit i hand självklar. Man kan välja det bästa av två världar och blanda kärnor optimerade för strömsnålhet respektive snabbhet på samma chip. Och under körningen dynamiskt använda den mest lämpade kärnan för aktuell uppgift.

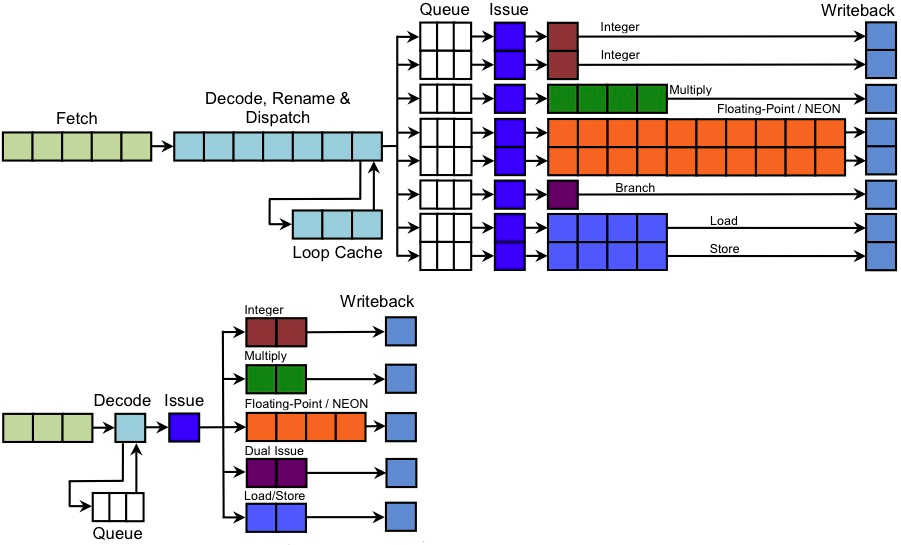

En Big Little-processor är strömsnål medan A7:an (underst) uppdaterar Facebook och vaktar telefonen. Den aktiverar tunga A15-kärnor (överst) när det är dags att rendera webbsidor eller spela Angry Birds. |

Marvell Armada 628 har två snabba kärnor och en snål.  TI Omap 5 har fyra snabba och två snåla.  Nvidia Tegra 3 har fyra snabba och en snål. |

Tekniken ger en större spännvidd i prestanda än vad man kan få genom att leka med spänning och frekvens. Samma klasser av optioner kan dock användas också här. Användaren kanske själv får välja mellan batteritid och prestanda. Eller så kan apparaten växla automatiskt mellan strömsnål och snabb när den kopplas in och ut ur elnätet.

Idén att skräddarsy kärnor för en uppgift är inte ny. Den är standard i systemkretsar, SoC:er. De dräller av specialiserade kärnor för video, grafik, kryptering, audio och annat, utöver dess generella CPU.

Men i nästa generation systemkretsar är alltså inte ens CPU:n en homogen multikärna.

Kärnor från brittiska Arm dominerar hittills helt kommersialiseringen av forskarnas idé. Det kommer en våg av Armprocessorer tillverkade i olika varianter enligt receptet.

2+1, 4+2 och 4+1 finns

Först ut var Marvell som hösten presenterade provexemplar av Armada 628. Den har två 1,5 GHz Armv7-kärnor för prestanda plus en strömsnål 624 MHz-kärna. Företaget refererar till den som en heterogen ”tricore”.

Nvidia tog fram sin första modell i smyg. När företagets fyrkärna Tegra 3 gick i massproduktion i höstas avslöjade företaget plötsligt att den hade en femte kärna. Av samma modell som de andra, men tillverkad i en strömsnål processteknik.

Nvidia kallar sin arkitektur för Variable Symmetric Multiprocessing (vSM) eller Four-plus-one. Den femte kärnan kallas ”batterisparkärna” eller bara ”kompanjon” och jobbar alltid ensam. Den används bland annat i standbyläge och vid musikspelning och videouppspelning – i det sistnämnda fallet drar ändå en separat accelerator det tunga lasset.

Texas Instruments Omap 5 har valt en kombination av fyra Cortex A9-kärnor och två Cortex M3-kärnor. Den ska släppas i volym under tredje kvartalet.

Nvidia, TI och Marvell har tagit fram egna lösningar genom att kombinera olika Arm-kärnor med varandra. Men mycket mer än så är inte känt om hur de fungerar under skalet.

I vintras lanserade Arm själv en färdig produkt som alla dess licenstagare kunde plocka upp. Arm berättar gärna hur den fungerar. Den heter Big Little och kombinerar Cortex A7- och A15-kärnor. A7 konstruerades med det direkta syftet att vara helt kompatibel med A15. Även om den också är en kandidat för enkelkärnor.

Cortex A15 är 1,9 till 3,0 gånger snabbare än Cortex A7 i olika prestandatester. Å andra sidan drar den mellan 2,3 och 3,8 gånger mer batteri för samma prestanda i samma tester.

2+2, 1+1, 4+4 alternativ

Cortex A7 använder tio steg i en in-orderrörledning för en flyttalsoperation medan A15 använder 23 i en out-of-orderrörledning.

Oftast pratar Arm om kombinationen 1+1 kärnor. Men kombinationen 2+2 skulle vara ett intressant alternativ för en billig mobiltelefon. Och 4+4 skulle också vara möjlig, liksom versioner med olika antal kärnor i klustren, som 4+1.

Oftast pratar Arm om kombinationen 1+1 kärnor. Men kombinationen 2+2 skulle vara ett intressant alternativ för en billig mobiltelefon. Och 4+4 skulle också vara möjlig, liksom versioner med olika antal kärnor i klustren, som 4+1.Big Little finns i två versioner. Den modell som kommer närmast forskarnas ideal kallas MP. Då är potentiellt alla kärnor aktiva samtidigt och programtrådar kan i princip fördelas dynamiskt på mest lämplig kärna. Vid låg belastning kan A15-kärnorna helt stängas ner.

Arm påpekar att MP-lösningen är dimensionerad för att kunna koppla in även en Mali-grafikkärna som också den hålls cachekoherent (kärnornas lokala cacheminnen får samma innehåll så att de vet att de jobbar med samma data – så fungerar multikärnor).

En enklare modell är att låta A7-klustret och A15-klustret turas om att ha hela ansvaret.

Den modellen kallas Task Migration. Vid växlingen ska alla aktiva programtrådar flyttas från det insomnande till det uppvaknande klustret. Det krävs att registerinnehåll och eventuella väntande interruptsignaler kopieras över. Enklast blir överlämningen om det finns lika många A7- som A15-kärnor.

Alla gillar Big Little

Överlämningen tar enligt Arm 20000 klockcykler (20 mikrosekunder i 1 GHz), och det är bara under en del av den tiden som processorn inte arbetar.

Det uppvaknande klustret startar i princip med tomt cacheminne, men det börjar direkt tjuvkika på det insomnande klustrets cache och hinner därmed delvis fyllas med data därifrån. Av samma skäl är det insomnande klustrets cache vaket några klockcykler efter att trådarna överlämnats.

Mjukvarumässigt ställer Big Little Task Migration enligt Arm bara till med kära porteringsbekymmer – operativsystemet får några nya fina prestandapunkter att välja mellan, samma typ av val som idag görs vid skalning av frekvens och spänning.

I MP-varianten finns också möjligheter att ta mer direkt kontroll över schemaläggningen – att låta alla kärnor vara vakna och detaljstyra vart trådar ska skickas. Detta är en större utmaning för operativsystemsmakarna och därmed något som kanske inte kommer i första generationen av Big Little-implementeringar.

Big Little tycks annars plockas upp närmast mangrant bland tillverkarna. Samsung kommer att använda den i sin Exynosfamilj nästa år. Freescale och Hisilicon har utlovat Big Little-processorer. Och ST-Ericsson, LG, Fujitsu och Broadcom har gjort tummen upp för produkten i pressreleaser.

Big Little ger Arm det bästa av två världar – hög prestanda och lång batteritid. I Cortex A15-processorer var batteritiden på väg att bli ett allvarligt problem. Att addera en snål Cortex A7-kärna som avlösare var en smart räddning av Arm.

Trumf mot Intel

I kampen mellan Intels processorfamilj Atom och Arm, är Big Little ett trumfkort. Med Cortex A7 som avlastning klarar Cortex A15 nu av att ta ytterligare ett steg upp mot Intel Atom i prestanda – och ändå ofta vara strömsnålare än till och med en gammal Cortex A8.

Priset Arm betalar är svart kisel – transistorer som tar upp plats utan att användas. Typiskt kommer A15-kärnorna att sova medan A7-kärnorna jobbar och tvärtom. Också detta är en orsak till att lösningen kommer just nu – när Moores lag gett oss tillräckligt många transistorer att leka med.

Konceptet Big Little används för kombinationen A7 och A15 och det är mobilprocessormakarna som är kunder. Men det finns tänkbara framtida tillämpningar bortom detta.

Effektutveckling handlar inte bara om energi, utan också om miniatyrisering – en mindre värmeutveckling möjliggör en mindre processorkapsel.

En server skulle kunna ha nytta av ett större effektspann – i serverhallar kostar det pengar både att mata in energi och att kyla bort den.

Nandan Nayampally |

–Tekniken är ju oberoende av arkitekturen. Den är säkerligen skalbar och du kommer antagligen att få se fler annonseringar vad det lider, säger Nandan Nayampally.