Zero Asic tar vid där Adapteva slutade men med ett lite annorlunda fokus, företaget ska bli ett designhus för asicar baserat på egenutvecklad IP. Dessutom sänker Zero Asic tröskeln för att ta fram komplexa systemkretsar genom att släppa sitt byggverktyg (build system) kallat SiliconCompiler, som open source.

Zero Asic tar vid där Adapteva slutade men med ett lite annorlunda fokus, företaget ska bli ett designhus för asicar baserat på egenutvecklad IP. Dessutom sänker Zero Asic tröskeln för att ta fram komplexa systemkretsar genom att släppa sitt byggverktyg (build system) kallat SiliconCompiler, som open source.

– Alla stora halvledarföretag har egenutvecklade build systems, de kan vara baserade på Perl, Make, C++ eller något annat, säger svenskättade Andreas Olofsson som grundat halvledarbolaget Zero Asic.

Han är nog mest känd för sitt tidigare bolag Adapteva som utvecklade och sålde parallellprocessorn Epiphany. Innan dess arbetade han på Analog Devices med att bland annat utveckla signalprocessorn TigerSharc. På senare år har han lett ett program för det amerikanska försvarsprogrammet Darpa inom AI, EDA, kapsling och superprocessorer.

2020 grundade han Zero Asic som kan ses som en fortsättning på Adapteva.

– Det är lite för tidigt att berätta om vad vi ska göra men framgångsrika asicföretag som IBM och LSI Logic var inte rena designhus utan hade alltid en intern plattform så att de kunde addera värde i form av egna IP-block.

Under årens lopp plöjde de ned miljardbelopp på att utveckla sin unika IP som sedan utgjorde basen i de kretsar de designade åt kunderna. För exempelvis LSI, som köptes av Avago 2014, var fokus datalagring och nätverk.

– Vi ska gå samma väg men det dröjer åtminstone ett år innan vi kan berätta om det.

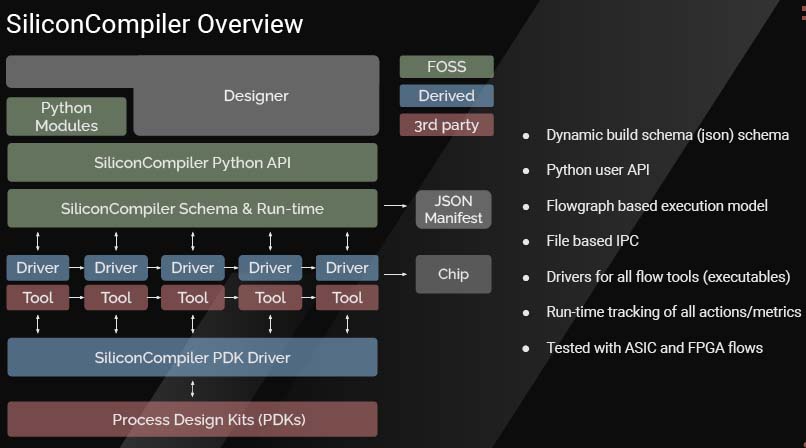

En del i förberedelsearbetet har varit att ta fram SiliconCompiler, ett verktyg som ligger mellan IP-blocken och EDA-verktygen, men som också kopplar till halvledarprocessen via det som kallas PDK och som gör det möjligt att översätta layouten till masker som sedan används för att tillverka kretsarna.

– Vi var tvungna att göra det för vår egen skull och bestämde oss för att göra det till open source. En del i beslutet beror på att vi fått stöd av RAMP-programmet från det amerikanska försvarsdepartementet, säger Andreas Olofsson.

Sedan SiliconCompiler lades upp på Github för drygt tre månader sedan har det laddats ned över 7000 gånger och fått över 400 github stars.

– Det är en liten community så det är väldigt mycket på tre månader och ett av de populäraste open sourceprojekten för hårdvara.

Det gäller särskilt i universitetsvärlden.

– Det sänker tröskeln för att designa kretsar. Idag kräver de flesta flöden att man kodar i TCL men de vill ha Python. Har man det blir det lockande.

Även om inte Zero Asic kommer att göra någon egen tape out i år finns det åtminstone tre andra projekt som ska göra det.

– Vi har kört hela vägen från System Verilog till GDS2 så vi vet att flödet fungerar. SiliconCompiler är väldigt moget för att vara ett open sourceverktyg, säger Andreas Olofsson.

Artikeln är tidigare publicerad i magasinet Elektroniktidningen. Artikeln är tidigare publicerad i magasinet Elektroniktidningen.Prenumerera kostnadsfritt! |

Företaget har fyra anställda idag med ytterligare tre på väg in. Målet är att vara 15 personer vid årets slut.

– Vi har ett kontor i Cambridge, MA, men vi ska bli ett globalt företag.

Sänker tröskeln för systemkretsar I mjukvaruvärlden har det länge funnits något som kallas för build-system, en programvara som underlättar kompilering och länkning av komplex mjukvara med många komponenter. En av de mer kända är Make, som funnits sedan 70-talet, men exempelvis Javascript har NPM, Python har PIP och Rust har Crates. I mjukvaruvärlden har det länge funnits något som kallas för build-system, en programvara som underlättar kompilering och länkning av komplex mjukvara med många komponenter. En av de mer kända är Make, som funnits sedan 70-talet, men exempelvis Javascript har NPM, Python har PIP och Rust har Crates.Mjuka IP-block för chipkonstruktion består av kod i System Verilog och fungerar i princip på samma sätt som källkod i programmering. Vid chip-design kan det också finnas ”hårda delar” där IP-blocken redan är färdiglayoutade för en viss tillverkningsprocess och inte går att modifiera. De som designat asicar och FPGA:er har saknat hjälpmedel som kan hantera alla IP-block ihop med valfria EDA-verktyg. Det gäller både kommersiella hjälpmedel och för open source. Konstruktörerna har istället fått lösa uppgiften på egen hand vilket lett till att alla större halvledarföretag utvecklat egna buildsystem som passat de verktyg som just de använder. Ofta har de lånat delar från Perl eller Unix, exempelvis skriptfunktioner eller batchkörningar. SiliconCompiler tar hand om allt detta och orkestrerar flödet av alla IP-block, mjuka såväl som hårda, så att bara de delar som ändrats skickas till ett visst EDA-verktyg för att göra exempelvis en syntetisering eller place & route för att skapa en färdig krets. – Ju fler filer man har desto mer tid tar det. Och ändrar man i en vill man inte kompilera om alla, säger Andreas Olofsson. Dessutom har det ett objektorienterat API baserat på Pyton vilket är särskilt populärt i universitetsvärlden. Förutom att koppla in EDA-verktyg behövs också koppling till det som kallas PDK, Process Design Kit. I praktiken är det en receptbok för hur man överför den färdiga layouten till alla lager i kislet. SiliconCompiler har till att börja med ett PDK för det amerikanska foundryt Skywaters 130 nm-process, det foundry som Google erbjuder shuttletillverking med. – Skywater är vad vi sagt offentligt men vi håller på att ta fram drivrutiner för två avancerade kommersiella noder. När det är klart ska användarna kunna välja process i det sista steget. SiliconCompiler går att köra lokalt men har också stöd för att köra i molnet. – Det är viktigt eftersom open source är väldigt fokuserat på Linux medan 99 procent av världen kör Windows eller Mac. Rent praktiskt kan man ha filerna lokalt på sin dator med Windows, MacOS eller Linux och sedan köra dem i molnet på SiliconCompiler för att därefter hämta hem resultatet. – Vi behövde ha Linux i mitten och löste det på det här sättet eftersom alla inte vill ha det lokalt. Dessutom passar det bra för universitetsvärlden. |