EMBEDDED WORLD Att den öppna cpu-arkitekturen RISC-V tillåter skräddarsydda instruktioner är en av dess stora styrkor, anser tjeckiska Codasip – och erbjuder verktygen för att backa upp möjligheten.

EMBEDDED WORLD Att den öppna cpu-arkitekturen RISC-V tillåter skräddarsydda instruktioner är en av dess stora styrkor, anser tjeckiska Codasip – och erbjuder verktygen för att backa upp möjligheten.

Inom RISC-V-ekosystemet blev Codasip först med att erbjuda en kommersiell implementation. Företaget tror sig dessutom fortfarande att vara ensamt om att erbjuda möjligheten att addera nya instruktioner.

|

| Roddy Urquhart |

– Om någon vill ha en RISC-V med DSP-funktionalitet så kan vi ordna det, säger Roddy Urquhart, affärsutvecklare på Codasip.

CPU-utvecklingsverktygen är Codasips huvudprodukt. Bland användarna finns bland annat israeliska Mobileye, som Intel just nu köper för en smärre förmögenhet.

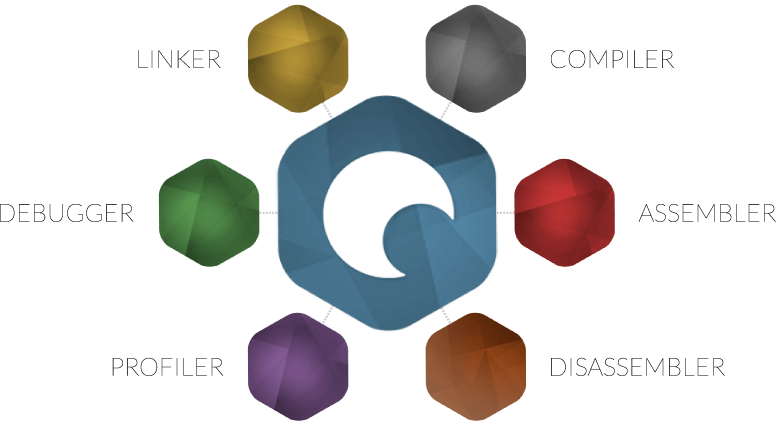

Codasip saluför dessutom ett antal CPU-kärnor som kan konfigureras och få nya instruktioner. Verktyget spottar inte bara ur sig designfiler utan dessutom färdiga C-kompilatorer och debuggers med stöd för Linux för din färska helt unika CPU.

Giganternas nya CPU |

|

Codasip är en aktör i det gryende ekosystemet kring RISC-V som är en CPU-arkitektur som är öppen källkod Vem som helst kan tillverka en egen processor som använder RISC-V-instruktionsuppsättningen, medan kommersiella alternativ som MIPS och ARM kräver royalities. RISC-V är långtifrån den första öppna cpu:n och rörelsen för öppen hårdvara är gammal. Men RISC-V har några av datorarkitekturvärldens giganter bakom sig och dessutom ett brett stöd från forskningsvärlden liksom från den kommersiella världen med jättar som Google, HP, Samsung, Qualcomm och NXP. Den har potential att bli en game-changer i elektronikvärlden likt Linux eller FreeRTSOS för operativsystem. Att det är öppen källkod betyder att det alltid kommer att finnas en second source, oavsett om din leverantör av verktyg eller kod lever kvar eller inte. – Om vi försvann skulle ändå folks investeringar i RISC-V inte vara bortkastade. |

Amerikanska kunden SecureRF, som säkrar upp IoT-prylar med asymmetrisk kryptering, adderade egna instruktioner för att snabba upp så kallade galoisoperationer.

En annan amerikansk kund är Sigma designs, liksom en ”ganska välkänd” fabless-tillverkare. I Japan är Sony LSI kund för en bildsensor.

Codasip blev först att erbjuda en kommersiell kärna i den nya gratisarkitekturen RISC-V. Den finns hos Codasip i två versioner, BK-III, BK-V, med tre respektive fem stegs pipeline. De kan bland annat konfigureras med stöd för multiplikation, flyttal, divsion, och så vidare.

Tensilica och Arc har stött egendefinerade instruktioner i ett par decennier, men just detta faktum är deras svaghet, enligt Codasip – deras teknik har åldrats.

RISC-V har ambitionen att täcka in hela spektrumet av processor från strömsnåla till kraftfulla, men tillsvidare rekommenderar Codasip ofta sina tre egna kärnor. Helium är liten strömsnål kärna, Titanium är en kraftfull VLIW-kärna för exempelvis bildbehandling och Cobalt är både snabb, snål och har litet fotavtryck.

Den stora fördelen med Berkeliumkärnorna idag är kanske just att de är RISC-V.

– Vi planerar en kraftfullare RISC-V senare i år, med kapacitet som en Cortex A5, ungefär.

RISC-V-kärnorna stöder Linux och snart även FreeRTOS.

Codasip är en avknoppning från universitetet i Brno, Tjeckien.